## HYGROSENS INSTRUMENTS

# **Serial Digital Interface of HYGROSENS ASIC**

Protocol of I<sup>2</sup>C Interface SPI Interface

#### **SERIAL DIGITAL INTERFACE**

#### Index

| Index                                           | 2 |

|-------------------------------------------------|---|

| Manufacturer Informations                       |   |

| I General Description                           | 3 |

| 2 I2C Protocol                                  | 5 |

| 3 Synchronous serial peripheral interface (SPI) |   |

| Interface Commands                              |   |

#### **Manufacturer Informations**

#### **Manufacturer Informations**

#### ## HYGROSENS INSTRUMENTS GmbH

Maybach Straße 2 Postfach 1054 79843 Löffingen 79840 Löffingen

Phone: 0049 7654 808969-0 Fax: 0049 7654 808969-9

Internet: <a href="www.hygrosens.com">www.hygrosens.com</a>

Email: <a href="mailto:info@hygrosens.com">info@hygrosens.com</a>

#### **Service and Orders**

Service and Orders

Phone: 0049 7654 808969-0 Fax: 0049 7654 808969-9

Internet: <a href="www.hygrosens.com">www.hygrosens.com</a>

Email: <a href="sales@hygrosens.com">sales@hygrosens.com</a>

**Technical Support and Calibration Service**

Phone: 0049 7654 808969-0 Fax: 0049 7654 808969-9

Internet: <a href="www.hygrosens.com">www.hygrosens.com</a>

Email: <a href="support@hygrosens.com">support@hygrosens.com</a>

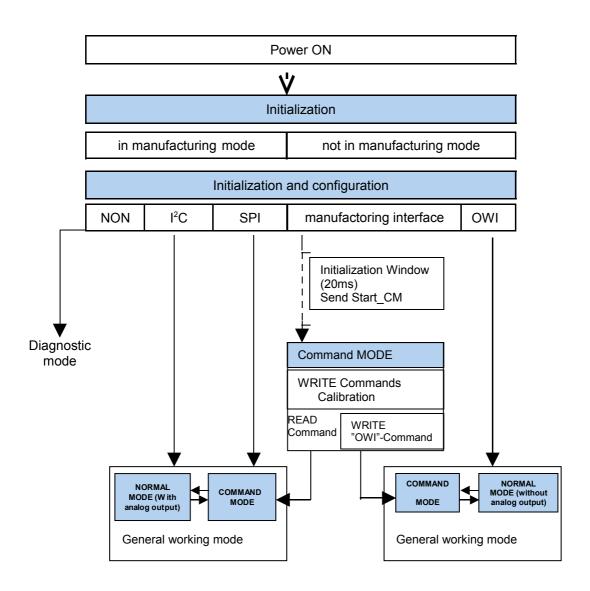

#### 1 General Description

The HYGROSENS ASIC includes a serial digital interface, which is able to communicate using two different communication protocols – I<sup>2</sup>C and SPI –communication. The serial digital interface allows the programming of the EEPROM to configure the application mode of the ASIC and to calibrate the conditioning equation. Furthermore it makes possible the read out of the conditioning result of measurand and both temperatures as digital 15 Bit values. The ASIC works always as slave. The used communication protocol has to be chosen by programming EEPROM. There are also commands to change the valid communication mode. Only one communication protocol is valid at one time. The implemented commands are available in all communication modes but are divided in two sets with different validity. Commands, which change the configuration of the device, are suppressed in "Normal Operation Mode" (NOM) and are available only after changing to "Command Mode" (CM). A nonconfigured device, identified by a CRC Error regarding EEPROM contents, starts up in a special mode so that communication by any of the available protocols is possible. After power-on a 20ms-time-slot is opened to start Service-communication. If no Service-communication is detected, the serial digital interface changed in a mode in which it can receive commands in I<sup>2</sup>C-mode as well as in SPI-mode. If it is necessary to read out data from a non-configured device (transmission by slave), the used communication protocol has to be explicitly defined by sending a certain command. Note that the HYGROSENS ASIC also do not send acknowledges in non-configured mode if I2C-communication is used. If the HYGROSENS ASIC receives a valid command at the serial digital interface the measurement cycle is interrupted because the internal micro-controller has to execute the requested command routine. An exception is a read-request. The HYGROSENS ASIC answers without interrupting the measurement cycle. This makes possible the read-out of the digital conditioning results during measurement cycle. A command consists of an address byte and a command byte. Additionally the commands for writing the EEPROM or its mirror in the RAM enclose two data bytes. This is independent from used communication protocol. To read data from the HYGROSENS ASIC (e.g. EEPROM contents) usually a certain command has to be sent to transfer this data into the output register of the serial interface. Thereafter the READ command consisting of the address byte with the read bit set is used to get this data. The data are transmitted continuously repeated as long as the master send the clock and do not abort by generating a stop condition. Again this is independent from used communication protocol. During the measurement cycle the HYGROSENS ASIC transfers the conditioning results into the output registers of the serial digital interface. There are three registers for humidity and both temperatures. The activation of these registers and consequently of the transmitted data have to be set by EEPROM programming. The results are sent in the sequence humidity, temperature 1 and temperature 2 according to the register activation if the master sends a read-request.

Fig. 1: Possible Communication Configuration

#### 2 I<sup>2</sup>C Protocol

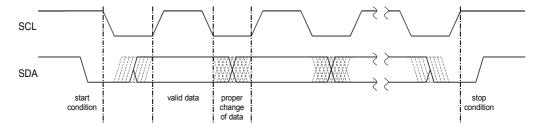

For I<sup>2</sup>C communication a data line (SDA) and a clock line (SCL) are required. The I<sup>2</sup>C protocol used is defined as follows:

#### Idle period

During inactivity of the bus SDA and SCL are pulled-up to supply voltage VDDA.

#### Start condition

A high to low transition on SDA while SCL is at high level indicates a start condition. Every command has to be initiated by a start condition sent by a master. A master can always generate a start condition.

#### Stop condition

A low to high transition on SDA while SCL is at high level indicates a stop condition. A command has to be closed by a stop condition to start processing the command routine inside the IC.

Fig. 2: Principles of I<sup>2</sup>C protocol

#### Valid data

Data is transmitted in Bytes (8 Bits) starting with the most significant bit (MSB). Each byte transmitted is followed by an acknowledge bit. Transmitted bits are valid if after a start condition SDA keeps at constant level during high period of SCL. The SDA level has to change only when clock signal at SCL is low.

#### **Acknowledge**

Acknowledge after transmitted byte is obligatory. The master must generate an acknowledge related clock pulse. The receiver (slave or master) pulls-down the SDA line during acknowledge clock pulse. If no acknowledge is generated by the receiver a transmitting slave will set inactive. A transmitting master can abort the transmission by generating a stop condition and may repeat the command.

A receiving master must signal the end of transfer to the transmitting slave by not generating an acknowledge related clock pulse at SCL.

The HYGROSENS ASIC as a slave changes to inactive interface mode during processing internal command routines started by a previously sent command.

#### Addressing

Every slave connected to the I<sup>2</sup>C-bus responds to a certain address. After generating the start condition the master sends the address byte containing a 7bit-address followed by a data direction bit (R/W). A '0' indicates a transmission from master to slave (WRITE), a '1' indicates a data request (READ).

The addressed slave answers with an acknowledge, all other slaves connected with the I<sup>2</sup>C-bus ignore this communication.

The general HYGROSENS ASIC slave address is 0x78 (7bit). As the address is completed with the R/W-Bit as LSB the address Byte (whole 8 bit) for reading data is 0xA1 for reading or 0xA0 for writing data to the ASIC.

By EEPROM programming it is possible to allocate and activate an additional arbitrary slave address to every single device. In this case the device recognizes communication on both addresses, on the general one and on the activated one.

#### Write operation

During transmission from master to slave (WRITE) after the address byte follows a command byte and, depending on the transmitted command, optional 2 data bytes. The internal micro-controller evaluates the received command and processes the related routine. The available commands are described in chapter 4.5.

|                    |                  |          |        |                 | optional |                              |        |                              |        |                   |

|--------------------|------------------|----------|--------|-----------------|----------|------------------------------|--------|------------------------------|--------|-------------------|

| start<br>condition | slave<br>address | R/W<br>0 | Α      | command<br>byte | Α        | 1 <sup>st</sup><br>data byte | Α      | 2 <sup>nd</sup><br>data byte | Α      | stop<br>condition |

| send by: master    |                  | slave    | master | slave           | master   | slave                        | master | slave                        | master |                   |

Fig. 3: Write operation I<sup>2</sup>C

#### **Read operation**

After a data request from master to slave by sending an address-byte including a set data direction bit the slave answers by sending data from the activated interface output registers. The master must generate the transmission clock on SCL, the acknowledges after each data byte (except after the last one) and finally the stop condition.

A data request is answered by the interface module itself and does consequently not interrupt the current process of the internal micro-controller. The data in the activated registers is sent continuously until a stop condition is detected, after transmitting all available data the slave starts repeating the data.

During running measurement cycle data is incessantly updated with conditioning results. To get other data from slave (e.g. EEPROM contents) usually a certain command has to be sent before the data request to initiate the transfer of this data to the interface output registers. This command does interrupt the current process of the internal microprocessor and consequently also a running measurement cycle.

|                       |                  |          |       |                  | optional |                  |        |                  |                   |  |

|-----------------------|------------------|----------|-------|------------------|----------|------------------|--------|------------------|-------------------|--|

| start<br>condition    | slave<br>address | R/W<br>1 | Α     | 1st<br>data byte | Α        | 2nd<br>data byte | Α      | nth<br>data byte | stop<br>condition |  |

| sent by: master slave |                  |          | slave | slave            | master   | slave            | master | slave            | Master            |  |

Fig. 4: Read operation I<sup>2</sup>C

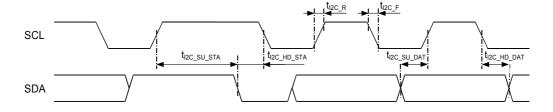

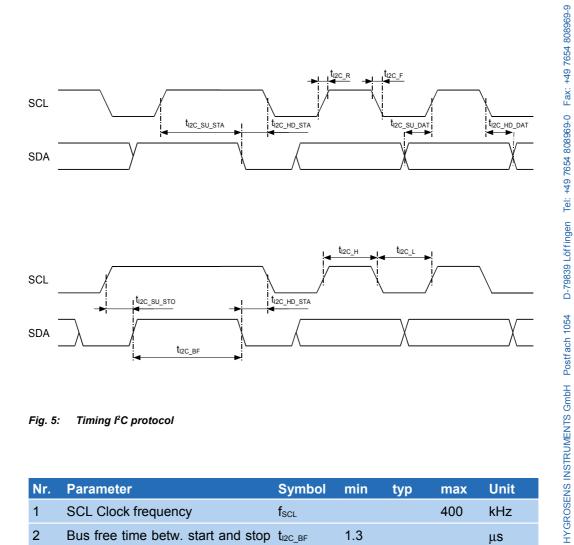

Fig. 5: Timing I<sup>2</sup>C protocol

| Nr. | Parameter                                        | Symbol                  | min | typ | max | Unit |

|-----|--------------------------------------------------|-------------------------|-----|-----|-----|------|

| 1   | SCL Clock frequency                              | f <sub>SCL</sub>        |     |     | 400 | kHz  |

| 2   | Bus free time betw. start and stop condition     | t <sub>I2C_BF</sub>     | 1.3 |     |     | μs   |

| 3   | Hold time start condition                        | t <sub>I2C_HD_STA</sub> | 0.6 |     |     | μs   |

| 4   | Setup time repeated start condition              | t <sub>I2C_SU_STA</sub> | 0.6 |     |     | μs   |

| 5   | Low period SCL/SDA                               | t <sub>I2C_L</sub>      | 1.3 |     |     | μs   |

| 6   | High period SCL/SDA                              | t <sub>I2C_H</sub>      | 0.6 |     |     | μs   |

| 7   | Data hold time                                   | t <sub>I2C_HD_DAT</sub> | 0   |     |     | μs   |

| 8   | Data setup time                                  | t <sub>I2C_SU_DAT</sub> | 0.1 |     |     | μs   |

| 9   | Rise time SCL/SDA                                | t <sub>I2C_R</sub>      |     |     | 0.3 | μs   |

| 10  | Fall time SCL/SDA                                | t <sub>I2C_F</sub>      |     |     | 0.3 | μs   |

| 11  | Setup time stop condition                        | t <sub>I2C_SU_STO</sub> | 0.6 |     |     | μs   |

| 12  | Noise interception SDA,<br>Spikes are suppressed | t <sub>I2C_NI</sub>     |     |     | 50  | ns   |

Table 1 Timing I<sup>2</sup>C protocol

Technische Änderungen vorbehalten!

### Example

Factory setting for configuation of I<sup>2</sup>C interface:

The following example is valid if the HYGROSENS USB Interface in conjunction with a standard terminal software is used:

t\_050 "set switch-off time to 50 ms"

t01200 "select trigger channel KS5V with a trigger time of 200 ms"

iwt7800172 "write command 0x72 to address 0x78 with trigger"

iw 7800152 "configure SIF to communication mode I<sup>2</sup>C"

iw\_7800171 "start Normal Operation Mode"

t00000 "turn OFF the trigger channel ==> KS5V = OFF"

The command 0x52 is configurating the serial interface for I<sup>2</sup>C communication. After starting the normal operating mode the serial interface is updated continously with the actual conditioned output values. The analog value is still available.

To read out the values

ir\_78004 "read four bytes in the order MSB humidity LSB humidity,

MSB temperature, LSB temperature"

+49 7654 808969-9

Fax:

+49 7654 808969-0

Tel:

D-79839 Löffingen

Postfach 1054

HYGROSENS INSTRUMENTS GmbH

#### 3 Synchronous serial peripheral interface (SPI)

During an SPI transfer, data is simultaneously transmitted (shifted out serially) and received (shifted in serially). A serial clock line synchronizes shifting and sampling of the information on the two serial data lines. A slave select line allows individual selection of a slave SPI device; slave devices that are not selected do not interfere with SPI bus activities. HYGROSENS ASIC's SPI slave interface supports all combinations of clock phase (CPHA) and polarity (CPOL). Slave CPOL and CPHA has to be programmed to master adjustments before beginning of transmission. RAM/EEPROM register 0x17<sub>hex</sub> contains initialization of SPI interface:

SFGSIF: SIFMD = interface mode SPI or I2C

SFGSIF: SPICKP = clock polarity CPOL SFGSIF: SPICKE = clock phase CPHA

#### **SPI Clock Phase and Polarity Controls**

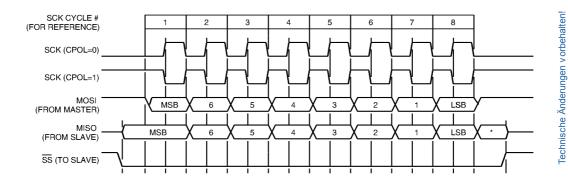

Software can select any of four combinations of serial clock (SCK) phase and polarity using two bits in the SPI control register (SPCR). The clock polarity is specified by the CPOL control bit, which selects an active high or active low clock and has no significant effect on the transfer format. The clock phase (CPHA) control bit selects one of two fundamentally different transfer formats.

#### **CPHA Equals Zero Transfer Format**

Fig. 12 shows a timing diagram of an SPI transfer where CPHA is zero. Two waveforms are shown for SCK: one for CPOL equals zero and another for CPOL equals one. The diagram may be interpreted as a master or slave timing diagram since the SCK, master in/slave out (MISO), and master out/slave in (MOSI) pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signals the output from the master. The /SS line is the slave select input to the slave.

Fig. 6: CPHA Equals Zero SPI Transfer Format – principle transfer illustration

Ausgabe 08/2008

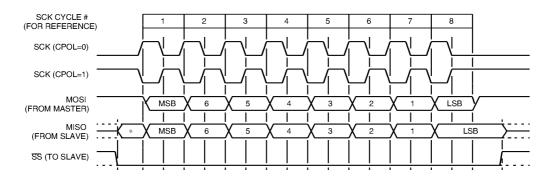

#### **CPHA Equals One Transfer Format**

Fig. 13 shows a timing diagram of an SPI transfer where CPHA is one. Two waveforms are shown for SCK: one for CPOL equals zero and another for CPOL equals one. The diagram may be interpreted as a master or slave timing diagram since the SCK, MISO, and MOSI pins are directly connected between the master and the slave. The MISO signal is the output from the slave, and the MOSI signal is the output from the master. The /SS line is the slave select input to the slave.

Fig. 7: CPHA Equals One SPI Transfer Format - principle transfer illustration

When CPHA equals zero, the /SS line must be negated and reasserted between each successive serial byte. Also, if the slave writes data to the SPI data register (SPDR) while /SS is active low, a write-collision error results.

When CPHA equals one, the /SS line may remain active low between successive transfers (can be tied low at all times). This format is sometimes preferred in systems having a single fixed master and a single slave driving the MISO data line.

#### **SPI Pin Signals**

There are four I/O pin signals associated with SPI transfers: the SCK, the MISO data line, the MOSI data line, and the active low /SS pin. When the master initiates a transfer, eight clock cycles are automatically generated on the SCK pin. The SCK pin is an input and the clock signal from the master synchronizes the data transfer between the master and slave devices. Slave devices ignore the SCK signal unless the /SS pin is active low. In both the master and slave SPI devices, data is shifted on one edge of the SCK signal and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI transfer protocol.

The MISO and MOSI data pins are used for transmitting and receiving serial data. At slave MOSI is the data input line, and MISO is the data output line. One by master selected slave device optionally drives data out its MISO pin to the MISO master pin. The automatic control of the direction of these pins makes reconfiguration through external logic unnecessary when a new device becomes the master.

The /SS pin behaves differently on master and slave devices. On a slave device, this pin is used to enable the SPI slave for a transfer. If the /SS pin of a slave is inactive (high), the device ignores SCK clocks and keeps the MISO output pin in the high-impedance state.

# Beginning and Ending SPI Transfers

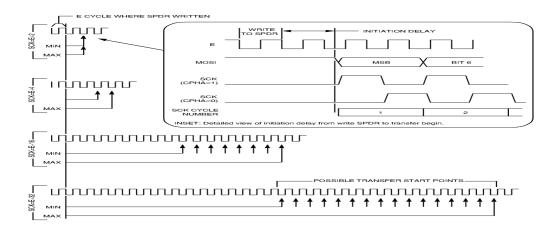

A transfer includes the eight SCK cycles plus an initiation period at the beginning and ending period of the transfer. The details of the beginning and ending periods depend on the CPHA format selected and whether the SPI is configured as a master or a slave. The initiation delay period is also affected by the SPI clock rate selection when the SPI is configured as a master.

It may be useful to refer to the transfer format illustrated in Fig. 12 and Fig. 13 to understand how the beginning and ending details fit into a complete transfer operation.

#### **Transfer Beginning Period (Initiation Delay)**

All SPI transfers are started and controlled by a master SPI device. As a slave the transfer to begin with the first SCK edge or the falling edge of /SS, depending on the CPHA format selected. When CPHA equals zero, the falling edge of /SS indicates the beginning of a transfer. When CPHA equals one, the first edge on the SCK indicates the start of the transfer. In either CPHA format, a transfer can be aborted by taking the /SS line high, which causes the SPI slave logic and bit counters to be reset. The SCK rate selected has no effect on slave operations since the clock from the master is controlling transfers.

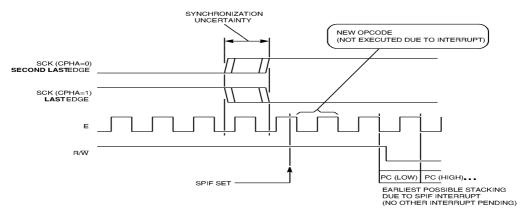

CPHA has no effect on the delay to the start of the transfer, but it does affect the initial state of the SCK signal. When CPHA equals zero, the SCK signal remains inactive for the first half of the first SCK cycle. When CPHA equals one, the first SCK cycle begins with an edge on the SCK line from its inactive to its active level. The SPI clock rate (selected by SPR[1:0]) affects the delay from the write to SPDR and the start of the SPI transfer (see Fig. 14). The internal SPI clock in the master is a free-running derivative of the internal MCU clock. Since the SPI clock is free-running, there is an uncertainty about the write operation to SPDR will occur relative to the slower SCK. This uncertainty causes the variation in the initiation delay shown in fig. 8.

Fig. 8: Delay from Write SPDR to Transfer Start (Master)

Fax: +49 7654 808969-9

Technische Änderungen vorbehalten!

+49 7654 808969-0 Fax: +49 7654 808969-9

<u>--</u>

D-79839 Löffingen

HYGROSENS INSTRUMENTS GmbH

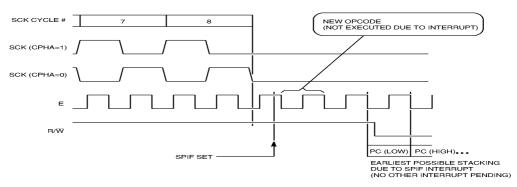

#### **Transfer Ending Period**

An SPI transfer is technically complete when the SPIF flag is set, but, depending on the configuration of the SPI system, there may be additional tasks. Because the SPI bit rate does not affect timing of the ending period, only the fastest rate will be considered in discussions of the ending period.

When the SPI is configured as a master, SPIF is set at the end of the eighth SCK cycle. When CPHA equals one, SCK is inactive for the last half of the eighth SCK cycle. Fig. 15 shows the transfer ending period for a master. The SCK waveforms in this figure show only the CPOL equals zero case, since clock polarity does not affect timing of the ending period.

Fig. 9: Transfer Ending for an SPI Master

When the SPI is operating as a slave, the ending period is different because the SCK line can be asynchronous to the MCU clocks of the slave and because the slave does not have access to as much information about SCK cycles as the master. For example, when CPHA equals one, where the last SCK edge occurs in the middle of the eighth SCK cycle, the slave has no way of knowing when the end of the last SCK cycle is. For these reasons, the slave considers the transfer complete after the last bit of serial data has been sampled, which corresponds to the middle of the eighth SCK cycle. A synchronization delay is required so the setting of the SPIF flag is properly positioned relative to the internal clock of the slave. Fig. 16 shows the ending period for a slave. The SCK waveforms in this figure show only the CPOL equals zero case, since clock polarity does not affect timing of the ending period.

Fig. 10: Transfer Ending for an SPI Slave

When CPHA equals zero, there is a potential problem that can be avoided by proper software but is sometimes overlooked. The SPIF flag is set at the end of a transfer, but the slave is not permitted to write new data to the SPDR while the /SS line is still low. If the master device is busy, the /SS line to the slave can remain low longer than the slave expects.

Technische Änderungen vorbehalten!

# Tel: +49 7654 808969-0 Fax: +49 7654 808969-9

HYGROSENS INSTRUMENTS GmbH Postfach 1054 D-79839 Löffingen

Technische Änderungen vorbehalten!

#### 4 Interface Commands

All implemented commands are available in all communication modes  $-\ l^2C$  and SPI. A received valid command interrupts the internal micro-controller and initiates the processing of a command routine.

| Com-<br>mand<br>(HEX) | Data   | Command             | Remarks                                                                                                                                                                                                 | Processing<br>time<br>System clock<br>2MHz |

|-----------------------|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 01                    |        | START_CYC_EEP       | Start measurement cycle including initialization from EEPROM                                                                                                                                            | 350μs                                      |

| 02                    |        | START_CYC_RAM       | Start measurement cycle including initialization from RAM                                                                                                                                               | 220μs                                      |

| 10 1F                 |        | READ_RAM0           | Read data from RAM address 00 0F Writes data from RAM to SIF Output Registers Usually followed by Read operation                                                                                        | 50μs                                       |

| 20 2F                 |        | READ_RAM1           | Read data from RAM address 10 1F Writes data from RAM to SIF Output Register Usually followed by Read operation                                                                                         | 50μs                                       |

| 30 3F                 |        | READ_EEP0           | Read data from EEPROM address 00 0F Writes data from EEPROM to SIF Output Register Usually followed by Read operation                                                                                   | 50μs                                       |

| 40 4F                 |        | READ_EEP1           | Read data from EEPROM address<br>10 . 1F<br>Writes data from EEPROM to SIF Output Register<br>Usually followed by Read operation                                                                        | 50μs                                       |

| 5*-comm               |        | change EEPROM or RA | M configuration, used for communication to devices                                                                                                                                                      | with unknown                               |

| 50                    |        | CFG_SIF_TO_OWI      | Configure SIF to Communication Mode OWI                                                                                                                                                                 | 50μs                                       |

| 51<br>55<br>59<br>5D  |        | CFG_SIF_TO_SPI      | Configure SIF to Communication Mode SPI 51 SET_SIF_2_SPI SPI (CKE = 0, CKP = 0) 55 SET_SIF_2_SPI SPI (CKE = 0, CKP = 1) 59 SET_SIF_2_SPI SPI (CKE = 1, CKP = 0) 5D SET_SIF_2_SPI SPI (CKE = 1, CKP = 1) | 50μs                                       |

| 52                    |        | CFG_SIF_TO_I2C      | Configure SIF to Communication Mode I <sup>2</sup> C                                                                                                                                                    |                                            |

| 60                    | 2 Byte | SET_DAC             | Set Output DAC to value defined by data bytes $[0x0 \dots 0x7FF]$                                                                                                                                       | 100μs                                      |

| 70                    |        | START_OM            | Start Open Mode In Open Mode the command set is restricted! Change to Command Mode is possible                                                                                                          | 50μs                                       |

| 71                    |        | START_NOM           | Start Normal Operation Mode (NOM)<br>In Normal Operation Mode the command set is<br>restricted!<br>Change to Command Mode or Open Mode is NOT<br>possible                                               |                                            |

| 72                    |        | START_CM            | Start Command Mode (CM) Complete command set! Change to Open Mode or Normal Operation Mode is possible                                                                                                  |                                            |

Table 2: Restricted command set for serial digital interface – commands are always valid

During processing time the digital serial interface (SIF) is disabled, transmitted commands are ignored. The processing time depends from the internal system clock frequency, which is usually 2MHz but is changeable by EEPROM programming. The commands are divided in two sets with different validity. Commands, which change the configuration of the device, are ignored in NOM and are available only after changing to CM.

| Com-<br>mand<br>(HEX)   | Data   | Command                   | Remarks                                                                                                  | Processing<br>time<br>System clock<br>2MHz /<br>EEPROM-<br>Progr. Steps |

|-------------------------|--------|---------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|

| 80 8F                   | 2 Byte | WRITE_RAM0                | Write data to RAM address 00 0F                                                                          | 50μs                                                                    |

| 90 9F                   | 2 Byte | WRITE_RAM1                | Write data to RAM address 10 1F                                                                          | 50μs                                                                    |

| A0 AF                   | 2 Byte | WRITE_EEP0                | Write data to EEPROM address 00 0F                                                                       | 12.5ms / 1                                                              |

| B0 BF                   | 2 Byte | WRITE_EEP1                | Write data to EEPROM address 10 1F                                                                       | 12.5ms / 1                                                              |

| C0                      |        | COPY_EEP2RAM              | Copy Contents of EEPROM to RAM Restores EEPROM Configuration in RAM                                      | 130μs                                                                   |

| C3                      |        | COPY_RAM2EEP              | Copy Contents of RAM to EEPROM Stores RAM Configuration to EEPROM (signature is copied without check!!!) | 400ms / 32                                                              |

| C8                      |        | GET_EEP_SIGN              | Calculates EEPROM Signature and output to SIF Output Register                                            | 150μs                                                                   |

| C9                      |        | GEN_EEP_SIGN              | <code>GET_EEP_SIGN</code> + write the Signature to <code>EEPROM</code> address <code>0x1D</code>         | 12.6ms / 1                                                              |

| CA                      |        | GET_RAM_SIGN              | Calculates RAM Signature and output to SIF Output Register                                               | 150μs                                                                   |

| СВ                      |        | GEN_RAM_SIGN              | GET_RAM_SIGN + write the Signature to RAM address 0x1D                                                   | 150μs                                                                   |

| CC                      |        | CLEAR_EEP                 | Clear EEPROM to 0x00000                                                                                  | 12.5ms / 1                                                              |

| CF                      |        | ROM_VERSION               | Read ROM version and write it to SIF Output Register Usually followed by Read operation                  | 50μs                                                                    |

| All "D*"-C<br>analog ou |        | ed for calibration proces | s, write raw conversion result to SIF Output Registers,                                                  | do not effect to                                                        |

| D0                      |        | START_AD_P                | Start cyclic A/D-conversion at channel Humidity P                                                        | 50μs                                                                    |

| D1                      |        | START_AD_T1               | Start cyclic A/D-conversion at channel Temperature T1                                                    | +<br>AD-                                                                |

| D2                      |        | START_AD_T2               | Start cyclic A/D-conversion at channel Temperature T2                                                    | conversion<br>time                                                      |

| D4                      |        | START_AD_PAZ              | Start cyclic A/D-conversion at channel Auto-Zero Humidity PAZ                                            |                                                                         |

| D5                      |        | START_AD_TAZ1             | Start cyclic A/D-conversion at channel Auto-Zero Temperature TAZ1                                        |                                                                         |

| D6                      |        | START_AD_TAZ2             | Start cyclic A/D-conversion at channel Auto-Zero Temperature TAZ2                                        |                                                                         |

| D8                      |        | START_AD_P_AZ             | Start cyclic A/D-conversion at channel Humidity P incl. Auto-Zero-Correction                             |                                                                         |

| D9                      |        | START_AD_T1_AZ            | Start cyclic A/D-conversion at channel Temperature T1 incl. Auto-Zero-Correction                         |                                                                         |

| DA                      |        | START_AD_T2_AZ            | Start cyclic A/D-conversion at channel Temperature T2 incl. Auto-Zero-Correction                         |                                                                         |

| DB                      |        | START_AD_CMV_AZ           | Start cyclic A/D-conversion at channel Common Mode Voltage CMV incl. Auto-Zero-Correction                |                                                                         |

Table 3: Additional command set for serial digital interface

Note: These commands are only available in CM.

CM is set by command START\_CM ( $0x72_{\text{hex}}$ ) as first command after power on.

The technical information in this document has been checked with adequate care at our end and is intended to inform about the product and its applications. The descriptions are not to be understood as assurance of the defined characteristics of the product and should be checked by the user for the intended application. Any possible industrial third party patent rights are to be considered.

Issued August 2008 - This documentation supersedes all previous editions.

© Copyright 2008 HYGROSENS INSTRUMENTS GmbH. All rights reserved.

No part of this documentation is allowed to be stored, reproduced, processed, duplicated or published in any form without prior written permission from the company HYGROSENS INSTRUMENTS GmbH.