LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

# DIGITAL LOCK FOR AUTOMOTIVE IGNITIONS

#### FEATURES:

- 5040 Four-Digit Combinations (for a 10 digit Keypad)

- Combinations are Hard-Wire Programmed

- Sense Input Enables Operation

- Save Memory Feature for Valet Parking

- Convenience Delay Controlled by External Capacitor

- Static or Momentary Lock Control Output

- Save Memory and Lock Status Outputs

- +5V to +18V Operation (Vss VDD)

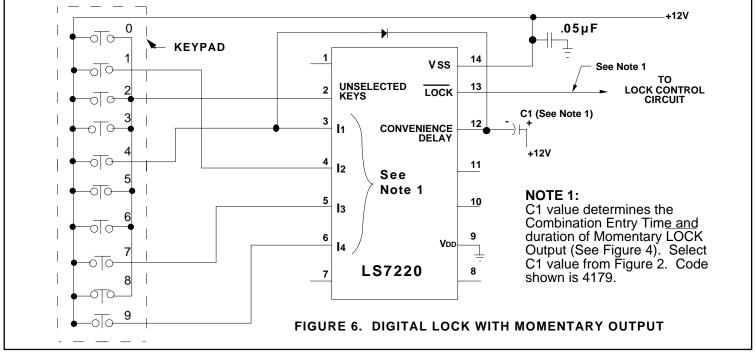

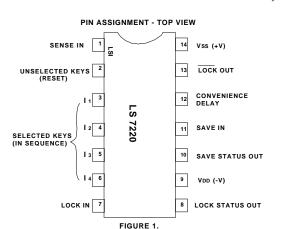

- LS7220 (DIP), LS7220-S (SOIC) See Figure 1

### **DESCRIPTION:**

The LS7220 is a MOS digital lock circuit. When wired to a ten-digit keypad, the circuit will recognize one four-digit combination out of a possible 5040 combinations.

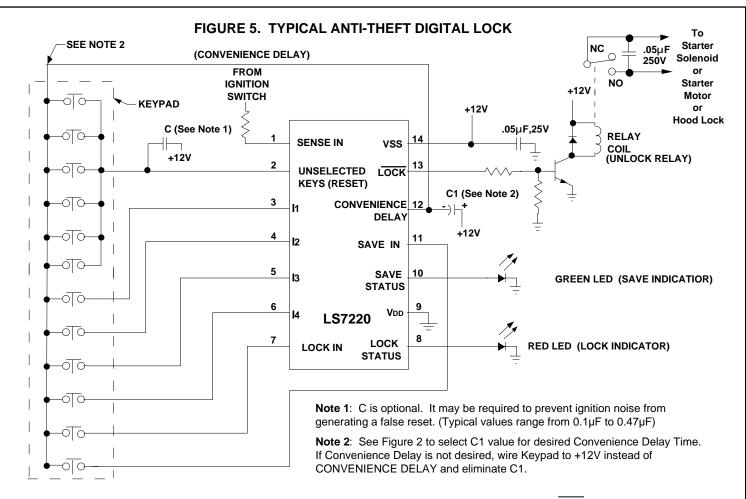

The LS7220 is configured with the features required for an Automotive Ignition Anti-Theft Digital Lock (See Figure 5). These features include Sense input which enables the IC, Save Memory for Valet Parking, Convenience Delay to maintain Unlock condition for short term interruptions of the Sense input and Save Status and Lock Status outputs which can be used for direct drive of LED indicators.

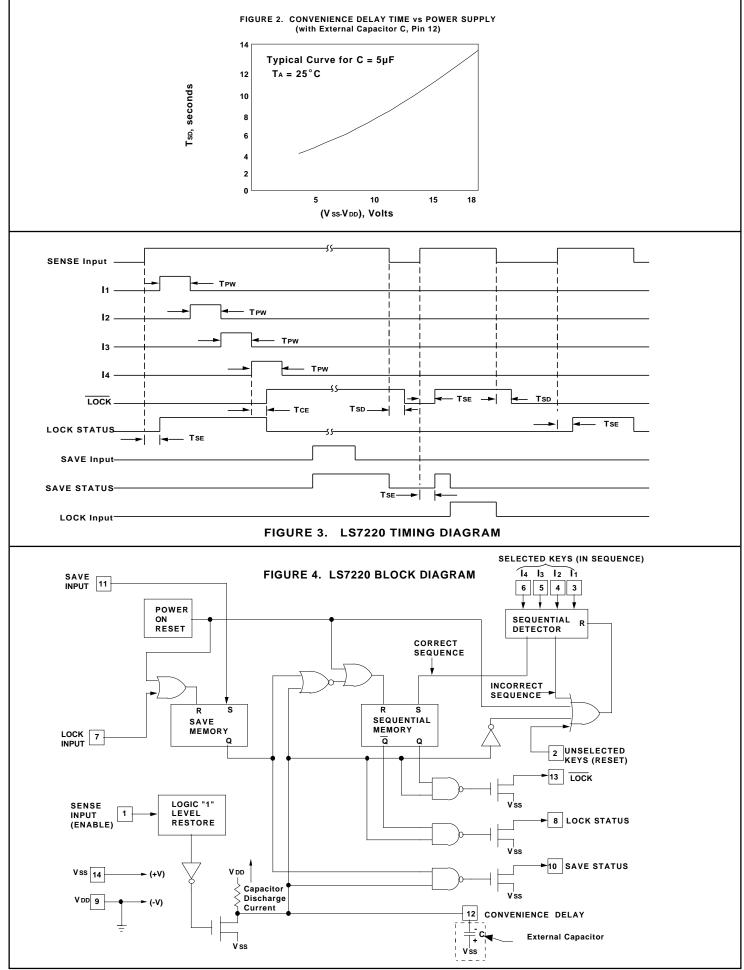

#### **OPERATING DESCRIPTION:** (Refer to Figures 2, 3, 4 and 5.)

When the Sense input goes high, the LS7220 is enabled. The Lock Status output turns on and Save Status and LOCK outputs remain off. When the programmed four-digit combination is entered from the keypad, in proper sequence, LOCK turns on and Lock Status turns off. If the Sense input is interrupted for a period of time greater than the Convenience Delay, the operating sequence must start over. If the Sense input is interrupted for a period of time less than the Convenience Delay, the operation of the LS7220 is unaffected. A momentary high at the Save input sets the Save Memory and causes the LS7220 to save an Unlock condition (Sequential Memory is set) for any time duration interruption of the Sense input (i.e., valet parking). The Save Status output turns on when Save Memory and return the LS7220 to normal operation.

**NOTE:** Using a 3 x 4 keypad, the \* key can be connected to the Lock input and the **#** key to the Save input. Lock Status and Save Status outputs can be used to drive red and green LED indicators, respectively.

# **INPUT/OUTPUT DESCRIPTION:** (Refer to Figure 4) **SENSE INPUT** (Pin 1)

A high at this input causes CONVENIENCE DELAY to transition high and enables recognition of the SELECTED KEYS when they are inputted in proper sequence. Control logic for LOCK, LOCK STATUS and SAVE STATUS outputs is also enabled. A low at this input keeps all outputs off and resets the Sequential Memory if Save Memory is not set.

VDD (Pin 9) Supply voltage negative terminal.

Vss (Pin 14) Supply voltage positive terminal.

January 2003

## UNSELECTED KEYS (RESET) INPUT (Pin 2)

A high at this input resets the Sequential Detector for the SELECTED KEYS inputs. This input must be wired to all digit keys which are not part of the Four-Digit Combination.

## SELECTED KEYS INPUTS (Pins 3, 4, 5, 6)

When these inputs are brought high in correct sequence, (i.e.,<u>I1, I2</u>, I3, I4) the Sequential Memory is set if SENSE input is high. LOCK output turns on and LOCK STATUS output turns off when the Sequential Memory is set.

### LOCK INPUT (Pin 7)

A high at this input resets the Save Memory. The SAVE STATUS output turns off when this occurs.

### LOCK STATUS OUTPUT (Pin 8)

This output is the complement of LOCK output when the SENSE input is high. See NOTE.

### SAVE STATUS OUTPUT (Pin 10)

This output turns on when Save Memory is set and SENSE input is high. See NOTE.

#### SAVE INPUT (Pin 11)

A high at this input sets the Save Memory. If Save Memory is set and Sequential Memory is set, the Save Memory will prevent the Sequential Memory from being reset as a result of a change at the SENSE Input. (See SAVE STATUS OUTPUT.)

# CONVENIENCE DELAY I/O (Pin 12)

An external capacitor placed on this pin will delay the effect of changes at the SENSE Input from affecting the outputs and the condition of the Sequential Detector and Sequential Memory. (See Figure 2)

### LOCK OUTPUT (Pin 13)

This output turns on when the Sequential Memory is set and SENSE input is high. See NOTE.

NOTE: Outputs are off when SENSE input is low.

| PARAMETER<br>DC Supply Voltage<br>Any Input Voltage<br>Operating Temperature<br>Storage Temperature |              | <b>SYMBOL</b><br>Vss - Vdd<br>Vin<br>Ta<br>Tstg | VALUE<br>+20<br>Vss - 20 to Vss + 0.<br>-25 to +85<br>-65 to +150 | UNIT<br>V<br>5 V<br>°C<br>°C |                         |                                                      |

|-----------------------------------------------------------------------------------------------------|--------------|-------------------------------------------------|-------------------------------------------------------------------|------------------------------|-------------------------|------------------------------------------------------|

| TRANSIENT CHARACTERIS<br>(TA = -25°C to +85°C, Vss = +                                              |              |                                                 |                                                                   |                              |                         |                                                      |

| PARAMETER<br>SENSE High Delay to<br>Outputs Enabled                                                 |              | SYMBOL<br>Tse                                   | MIN<br>-                                                          | <b>MAX</b><br>1              | UNIT<br>µs              | <b>CONDITION</b><br>No external<br>capacitor, Pin 12 |

| SENSE Low Delay to<br>Outputs Disabled                                                              |              | Tsd                                             | -                                                                 | 10                           | μs                      | No external<br>capacitor, Pin 12                     |

| Input Pulse Widths<br>(except SENSE)                                                                |              | Tpw                                             | 25                                                                | -                            | μs                      | -                                                    |

| Valid Combination Entry to<br>LOCK Output Enabled                                                   |              | Тсе                                             | -                                                                 | 10                           | μs                      | SENSE High                                           |

| DC ELECTRICAL CHARACT<br>(All voltages referenced to VD                                             |              |                                                 | ss otherwise specific                                             | ed.)                         | Vss voltages            | = 5V, 9V, 12V, 15V, 18V                              |

| PARAMETER                                                                                           | SYME         | BOL MIN                                         | Μ                                                                 | АХ                           | UNIT                    | CONDITION                                            |

| Supply Voltage<br>Supply Current                                                                    | Vss<br>Iss   | +5<br>-                                         | -<br>20, 30, 40                                                   | -18<br>, 50, 70              | V<br>µA                 | -<br>Vss voltages                                    |

| *INPUT VOLTAGES:                                                                                    |              |                                                 |                                                                   |                              |                         |                                                      |

| SENSE Low<br>SENSE High                                                                             | Vi∟<br>Viн   | 0<br>3.5, 5.5, 6.5, 9, 11.                      | 2, 3, 4,<br>5                                                     | 6, 8.5<br>√ss                | V<br>V                  | Vss voltages<br>Vss voltages                         |

| CONVENIENCE DELAY Low<br>CONVENIENCE DELAY High                                                     |              | -<br>0.7Vss                                     | 0.                                                                | 3Vss<br>-                    | -                       | Typical<br>Typical                                   |

| All Other Inputs:                                                                                   | .,           |                                                 |                                                                   |                              |                         |                                                      |

| Low<br>High                                                                                         | Vi∟<br>Vi⊦   | 0<br>Vss - 1                                    |                                                                   | ss - 3<br>√ss                | V<br>V                  | -                                                    |

| *NOTE 1: All inputs have pull<br>OUTPUT CURRENT:<br>***LOCK STATUS<br>Source Current<br>Vo = +1.7V  | down r<br>Io | esistors to VDD. Typic<br>0.4, 2.5, 5, 9, 14    |                                                                   | is 12µA witł<br>2, 20, **30  | n input at Vss (\<br>mA | /ss - Vdd = +12V)<br>Vss voltages                    |

| ***SAVE STATUS<br><b>Source Current</b><br>Vo = +1.7V                                               | lo           | 0.8, 5, 10, 18, 28                              | 2.6, 12, 2                                                        | 4, **30, **30                | mA                      | Vss voltages                                         |

| CONVENIENCE DELAY                                                                                   | lo           | 0.1, 0.5, 0.7, 1, 1.2                           | 0.5, 1.1,                                                         | 1.6, 2.1, 2.4                | mA                      | Vss voltages                                         |

| LOCK                                                                                                | lo           | 1.3, 6.5, 9.1, 13, 15                           | .6 6.5, 14.7,                                                     | 21, 27.3, **3                | 30 mA                   | Vss voltages                                         |

|                                                                                                     | CIN          | -                                               |                                                                   | 10                           | pF                      | -                                                    |

| Inupt Capacitance                                                                                   |              |                                                 |                                                                   |                              |                         |                                                      |

A typical automotive anti-theft digital lock circuit is shown in Figure 5. When the Ignition Switch is turned on the SENSE input (Pin 1) goes high and the circuit is ready to accept the unlocking input sequence at 11, 12, 13 and 14 (Pins 3, 4, 5 and 6, respectively). If the keys associated with these inputs are depressed exactly in sequence, the LOCK output (Pin 13) turns ON and the Unlock Relay is energized. This state is indicated by the OFF condition of the LOCK STATUS output (Pin 8) which turns the red LED OFF (indicates unlock condition). If the keys are depressed in any sequence other than as described above, the internal sequential detector resets and the entire sequence must be repeated (See Figure 4).

In order to save the ON condition of the LOCK output before the ignition switch is turned Off (i.e., when the SENSE input becomes low) the key associated with the SAVE input (Pin 11) has to be depressed. The "SAVE" status is indicated by a high at the SAVE STATUS output (Pin 10), which turns the green LED On. If the ignition switch is turned Off when the green LED is On, all the output status are preserved in the internal memory, so that when the ignition switch is turned on again there is no need to go through the input sequence again. This feature could be used for valet parking and garage service.

Status saving may be cancelled by depressing the LOCK input key followed by turning the ignition switch Off for a time greater than the CONVENIENCE DELAY (See Figure 2). This also turns OFF the LOCK output.