# Universal Serial Bus Type-C Cable and Connector Specification

Revision 1.2 March 25, 2016

Release 1.2 March 25, 2016

## Copyright © 2014-2016, USB 3.0 Promoter Group: Hewlett-Packard Company, Intel Corporation, Microsoft Corporation, Renesas, STMicroelectronics, and Texas Instruments All rights reserved.

NOTE: Adopters may only use the USB Type-C™ cable and connector to implement USB or third party functionality as expressly described in this Specification; all other uses are prohibited.

LIMITED COPYRIGHT LICENSE: The USB 3.0 Promoters grant a conditional copyright license under the copyrights embodied in the USB Type-C Cable and Connector Specification to use and reproduce the Specification for the sole purpose of, and solely to the extent necessary for, evaluating whether to implement the Specification in products that would comply with the specification. Without limiting the foregoing, use of the Specification for the purpose of filing or modifying any patent application to target the Specification or USB compliant products is not authorized. Except for this express copyright license, no other rights or licenses are granted, including without limitation any patent licenses. In order to obtain any additional intellectual property licenses or licensing commitments associated with the Specification a party must execute the USB 3.0 Adopters Agreement. NOTE: By using the Specification, you accept these license terms on your own behalf and, in the case where you are doing this as an employee, on behalf of your employer.

#### INTELLECTUAL PROPERTY DISCLAIMER

THIS SPECIFICATION IS PROVIDED TO YOU "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE. THE AUTHORS OF THIS SPECIFICATION DISCLAIM ALL LIABILITY, INCLUDING LIABILITY FOR INFRINGEMENT OF ANY PROPRIETARY RIGHTS, RELATING TO USE OR IMPLEMENTATION OF INFORMATION IN THIS SPECIFICATION. THE PROVISION OF THIS SPECIFICATION TO YOU DOES NOT PROVIDE YOU WITH ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS.

All implementation examples and reference designs contained within this Specification are included as part of the limited patent license for those companies that execute the USB 3.0 Adopters Agreement.

USB Type-C<sup>™</sup> and USB-C<sup>™</sup> are trademarks of the Universal Serial Bus Implementers Forum (USB-IF). All product names are trademarks, registered trademarks, or service marks of their respective owners.

#### CONTENTS

| Spe            | cificat | tion Wo | rk Group Chairs / Specification Editors                                                     | 11 |  |

|----------------|---------|---------|---------------------------------------------------------------------------------------------|----|--|

| Spe            | cificat | tion Wo | rk Group Contributors                                                                       | 11 |  |

| Pre            | -Relea  | se Draf | t Industry Reviewing Companies That Provided Feedback                                       | 13 |  |

| Rev            | ision   | History |                                                                                             | 14 |  |

| 1 Introduction |         |         |                                                                                             |    |  |

| 1.1 Purpose    |         |         |                                                                                             |    |  |

|                | 1.2     | •       |                                                                                             |    |  |

|                | 1.3     | •       | d Documents                                                                                 |    |  |

|                | 1.4     |         | ntions                                                                                      |    |  |

|                |         | 1.4.1   | Precedence                                                                                  | 16 |  |

|                |         | 1.4.2   | Keywords                                                                                    | 16 |  |

|                |         | 1.4.3   | Numbering                                                                                   | 17 |  |

|                | 1.5     | Terms   | and Abbreviations                                                                           | 17 |  |

| 2              | Over    | view    |                                                                                             | 20 |  |

|                | 2.1     | Introd  | uction                                                                                      | 20 |  |

|                | 2.2     | USB Ty  | pe-C Receptacles, Plugs and Cables                                                          | 21 |  |

|                | 2.3     | Config  | uration Process                                                                             | 22 |  |

|                |         | 2.3.1   | Source-to-Sink Attach/Detach Detection                                                      | 23 |  |

|                |         | 2.3.2   | Plug Orientation/Cable Twist Detection                                                      | 23 |  |

|                |         | 2.3.3   | Initial Power (Source-to-Sink) Detection and Establishing the (Host-to-Device) Relationship |    |  |

|                |         | 2.3.4   | USB Type-C VBUS Current Detection and Usage                                                 |    |  |

|                |         | 2.3.5   | USB PD Communication                                                                        |    |  |

|                |         | 2.3.6   | Functional Extensions                                                                       | 25 |  |

|                | 2.4     | VBUS    |                                                                                             | 25 |  |

|                | 2.5     | Vconn   |                                                                                             | 25 |  |

|                | 2.6     | Hubs    |                                                                                             | 26 |  |

| 3              | Mech    | anical  |                                                                                             | 27 |  |

|                | 3.1     | Overvi  | ew                                                                                          | 27 |  |

|                |         | 3.1.1   | Compliant Connectors                                                                        | 27 |  |

|                |         | 3.1.2   | Compliant Cable Assemblies                                                                  | 27 |  |

|                |         | 3.1.3   | Compliant USB Type-C to Legacy Cable Assemblies                                             | 27 |  |

|                |         | 3.1.4   | Compliant USB Type-C to Legacy Adapter Assemblies                                           | 28 |  |

|                | 3.2     | USB Ty  | pe-C Connector Mating Interfaces                                                            | 28 |  |

|                |         | 3.2.1   | Interface Definition                                                                        | 28 |  |

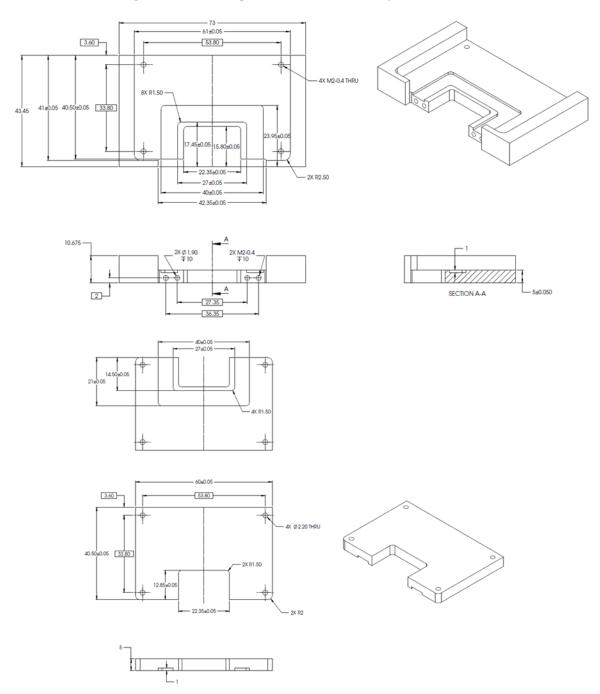

|                |         | 3.2.2   | Reference Designs                                                                           | 48 |  |

|                |         | 3.2.3   | Pin Assignments and Descriptions                                                            | 55 |  |

|                | 3.3     | Cable ( | Construction and Wire Assignments                                                           | 56 |  |

|                |         | 3.3.1   | Cable Construction (Informative)                                                            | 56 |  |

|                |         | 3.3.2   | Wire Assignments                                                                            |    |  |

|                |         | 3.3.3   | Wire Gauges and Cable Diameters (Informative)                                               | 59 |  |

4

| 3.4  | Standa  | rd USB Type-C Cable Assemblies                                    | 61    |

|------|---------|-------------------------------------------------------------------|-------|

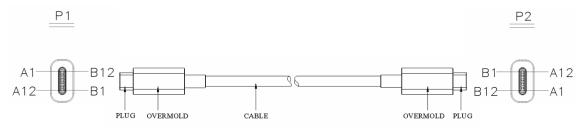

|      | 3.4.1   | USB Full-Featured Type-C Cable Assembly                           | 61    |

|      | 3.4.2   | USB 2.0 Type-C Cable Assembly                                     | 62    |

|      | 3.4.3   | USB Type-C Captive Cable Assemblies                               | 63    |

| 3.5  | Legacy  | Cable Assemblies                                                  | 63    |

|      | 3.5.1   | USB Type-C to USB 3.1 Standard-A Cable Assembly                   | 64    |

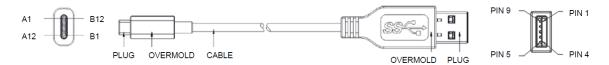

|      | 3.5.2   | USB Type-C to USB 2.0 Standard-A Cable Assembly                   | 65    |

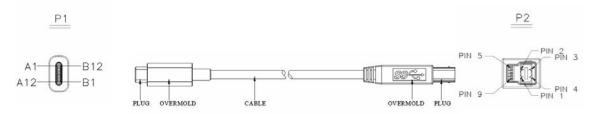

|      | 3.5.3   | USB Type-C to USB 3.1 Standard-B Cable Assembly                   | 66    |

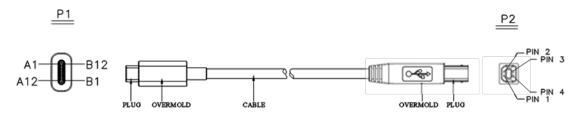

|      | 3.5.4   | USB Type-C to USB 2.0 Standard-B Cable Assembly                   | 67    |

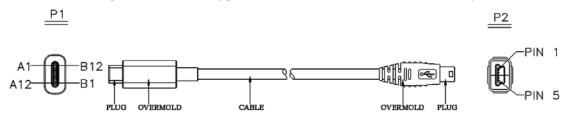

|      | 3.5.5   | USB Type-C to USB 2.0 Mini-B Cable Assembly                       | 68    |

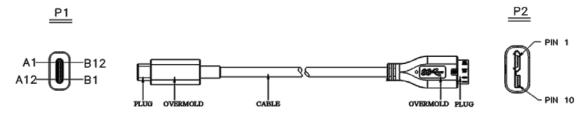

|      | 3.5.6   | USB Type-C to USB 3.1 Micro-B Cable Assembly                      | 69    |

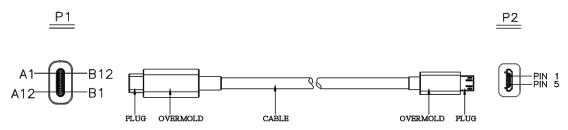

|      | 3.5.7   | USB Type-C to USB 2.0 Micro-B Cable Assembly                      | 70    |

| 3.6  | Legacy  | Adapter Assemblies                                                | 70    |

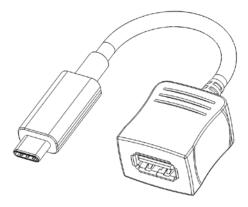

|      | 3.6.1   | USB Type-C to USB 3.1 Standard-A Receptacle Adapter Assemble      | ly 71 |

|      | 3.6.2   | USB Type-C to USB 2.0 Micro-B Receptacle Adapter Assembly         | 72    |

| 3.7  | Electri | cal Characteristics                                               | 74    |

|      | 3.7.1   | Raw Cable (Informative)                                           | 74    |

|      | 3.7.2   | USB Type-C to Type-C Passive Cable Assemblies (Normative)         | 75    |

|      | 3.7.3   | Mated Connector (Informative)                                     | 88    |

|      | 3.7.4   | USB Type-C to Legacy Cable Assemblies (Normative)                 | 91    |

|      | 3.7.5   | USB Type-C to USB Legacy Adapter Assemblies (Normative)           | 95    |

|      | 3.7.6   | Shielding Effectiveness Requirements (Normative)                  | 97    |

|      | 3.7.7   | DC Electrical Requirements (Normative)                            | 99    |

| 3.8  | Mecha   | nical and Environmental Requirements (Normative)                  | . 102 |

|      | 3.8.1   | Mechanical Requirements                                           | . 102 |

|      | 3.8.2   | Environmental Requirements                                        | . 108 |

| 3.9  | Dockin  | g Applications (Informative)                                      | . 109 |

| 3.10 | Implen  | nentation Notes and Design Guides                                 | . 110 |

|      | 3.10.1  | EMC Management (Informative)                                      | . 110 |

|      | 3.10.2  | Stacked and Side-by-Side Connector Physical Spacing (Informative) | 112   |

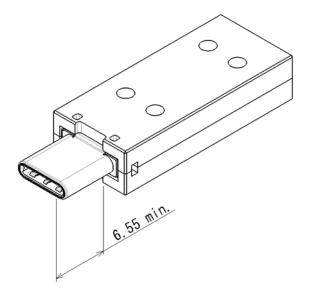

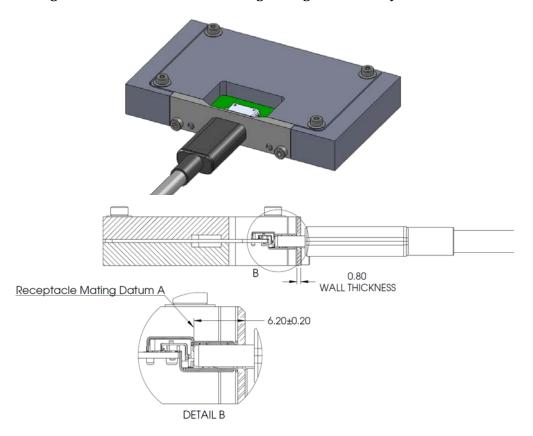

|      | 3 10 3  | Cable Mating Considerations (Informative)                         |       |

| Func |         | cable Matring Constitutions (finormative)                         |       |

|      |         |                                                                   |       |

| 4.1  | •       | SummaryPin Descriptions                                           |       |

| 4.2  | _       |                                                                   |       |

|      | 4.2.1   | SuperSpeed USB Pins                                               |       |

|      | 4.2.2   | USB 2.0 Pins                                                      |       |

|      | 4.2.3   | Auxiliary Signal Pins                                             |       |

|      | 4.2.4   | Power and Ground Pins                                             |       |

| 4.0  | 4.2.5   | Configuration Pins                                                |       |

| 4.3  |         | nd Use (SBU)                                                      |       |

| 4.4  |         | and Ground                                                        |       |

|      | 4.4.1   | IR Drop                                                           |       |

|      | 4.4.2   | VBUS                                                              | . 117 |

|   |                      | 4.4.3           | VCONN                                                               | 118 |

|---|----------------------|-----------------|---------------------------------------------------------------------|-----|

|   | 4.5                  | Configu         | uration Channel (CC)                                                | 120 |

|   |                      | 4.5.1           | Architectural Overview                                              | 120 |

|   |                      | 4.5.2           | CC Functional and Behavioral Requirements                           | 133 |

|   |                      | 4.5.3           | USB Port Interoperability Behavior                                  | 155 |

|   | 4.6                  | Power.          |                                                                     | 166 |

|   |                      | 4.6.1           | Power Requirements during USB Suspend                               | 167 |

|   |                      | 4.6.2           | VBUS Power Provided Over a USB Type-C Cable                         | 168 |

|   | 4.7                  |                 | ıbs                                                                 |     |

|   | 4.8                  | Charge          | rs                                                                  |     |

|   |                      | 4.8.1           | DFP as a Power Source                                               |     |

|   |                      | 4.8.2           | Non-USB Charging Methods                                            |     |

|   |                      | 4.8.3           | Sinking Host                                                        |     |

|   |                      | 4.8.4           | Sourcing Device                                                     |     |

|   |                      | 4.8.5           | Charging a System with a Dead Battery                               |     |

|   | 4.9                  |                 | onically Marked Cables                                              |     |

|   | 4.10                 |                 | Powered Accessories                                                 |     |

|   | 4.11                 |                 | eter Values                                                         |     |

|   |                      |                 | Termination Parameters                                              |     |

|   |                      |                 | Timing Parameters                                                   |     |

| _ | Euma                 |                 | Voltage Parameters<br>ktensions                                     |     |

| 5 |                      |                 |                                                                     |     |

|   | 5.1                  |                 | ate Modes                                                           |     |

|   |                      | 5.1.1           | Alternate Mode Architecture                                         |     |

|   |                      | 5.1.2           | Alternate Mode Requirements                                         |     |

|   |                      | 5.1.3           |                                                                     |     |

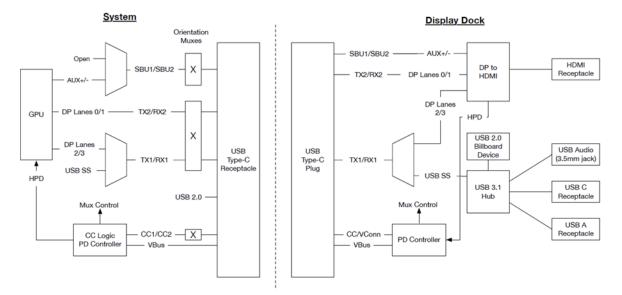

|   | <b>г</b> 2           | 5.1.4           | Example Alternate Mode – USB DisplayPort™ Dock                      |     |

|   | 5.2                  | мападо<br>5.2.1 | ed Active Cables                                                    |     |

|   |                      | 5.2.1           | Requirements for Managed Active Cables that respond to SOP' SOP"    |     |

|   |                      | 5.2.2           | Cable Message Structure                                             |     |

|   |                      | 5.2.3           | Modal Cable Management                                              |     |

| A | Audio                | o Adapte        | er Accessory Mode                                                   |     |

|   | A.1.                 | -               | ew                                                                  |     |

|   | A.2.                 |                 |                                                                     |     |

|   | A.3.                 |                 | cal Requirements                                                    |     |

|   | A.4.                 |                 | le Implementations                                                  |     |

|   |                      | A.4.1.          | Passive 3.5 mm to USB Type-C Adapter – Single Pole Detection Switch |     |

|   |                      | A.4.2.          | 3.5 mm to USB Type-C Adapter Supporting 500 mA Charge-              |     |

|   |                      |                 | Through                                                             |     |

| В | Debug Accessory Mode |                 |                                                                     | 199 |

|   | B.1.                 | Overvi          | ew                                                                  | 199 |

|   | B.2.                 | Functio         | onal                                                                | 199 |

|            | B.2.1.    | Signal Summary                                                                             | 200       |

|------------|-----------|--------------------------------------------------------------------------------------------|-----------|

|            | B.2.2.    | Port Interoperability                                                                      | 200       |

|            | B.2.3.    | Debug Accessory Mode Entry                                                                 | 200       |

|            | B.2.4.    | Connection State Diagrams                                                                  |           |

|            |           | DTS Port Interoperability Behavior                                                         |           |

|            | B.2.5.    |                                                                                            |           |

|            | B.2.6.    | Orientation Detection                                                                      |           |

| B.3.       | Securit   | y/Privacy Requirements:                                                                    | 220       |

| C USB 7    | Type-C D  | Digital Audio                                                                              | 221       |

|            |           |                                                                                            |           |

|            |           | FIGURES                                                                                    |           |

| Figure 2-1 | USB Ty    | pe-C Receptacle Interface (Front View)                                                     | 20        |

| Figure 2-2 | USB Ful   | ll-Featured Type-C Plug Interface (Front View)                                             | 21        |

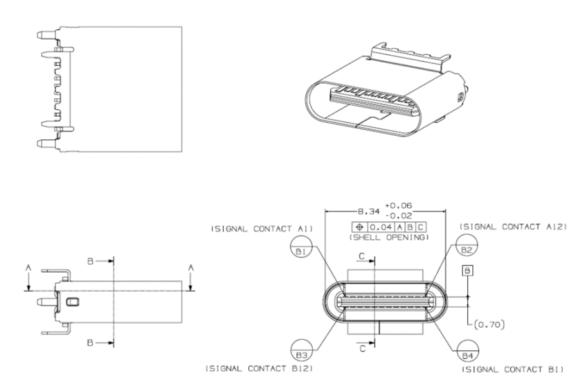

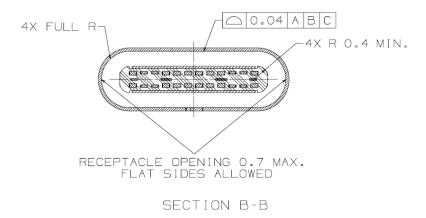

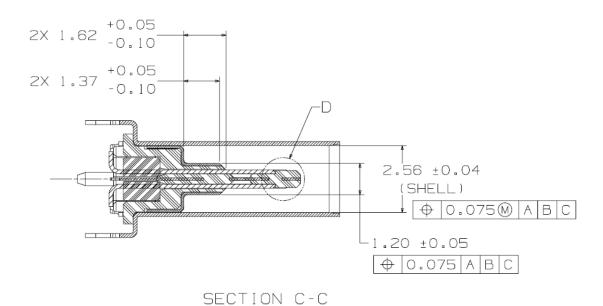

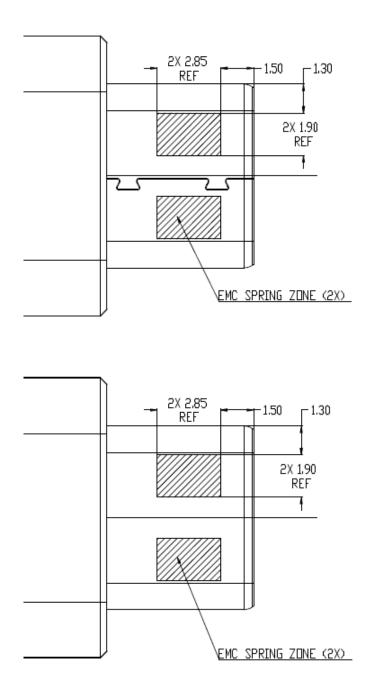

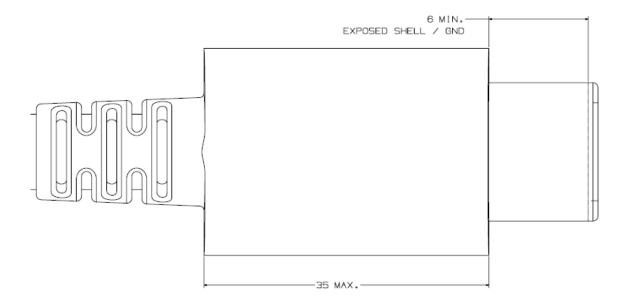

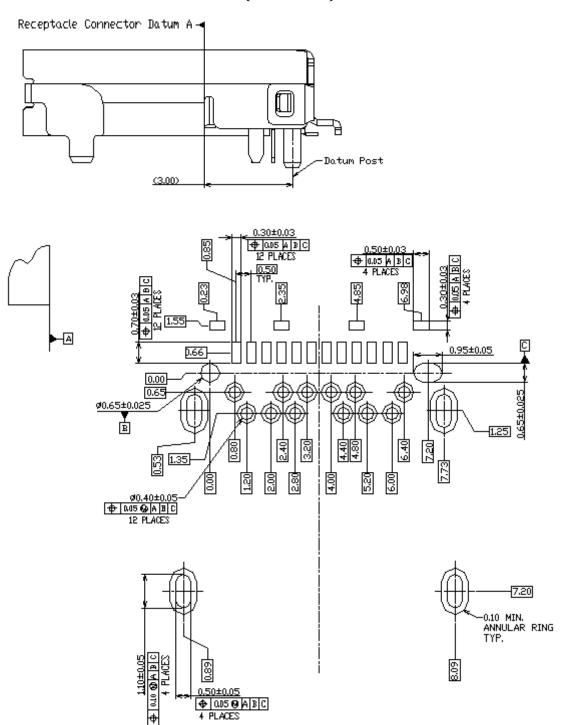

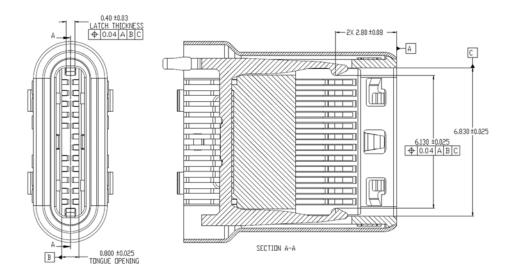

|            |           | pe-C Receptacle Interface Dimensions                                                       |           |

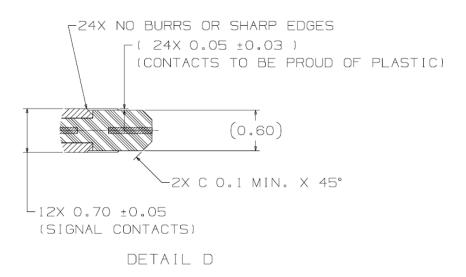

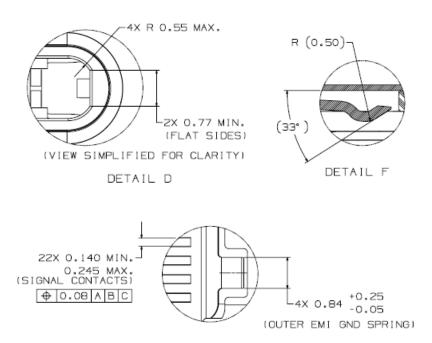

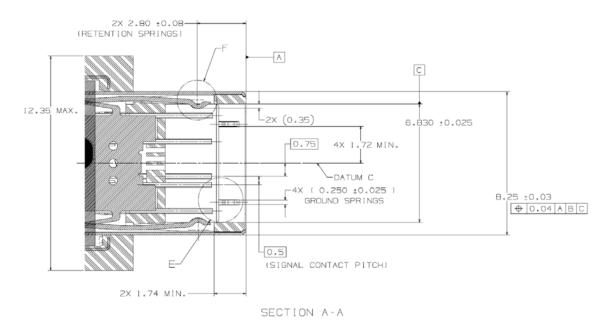

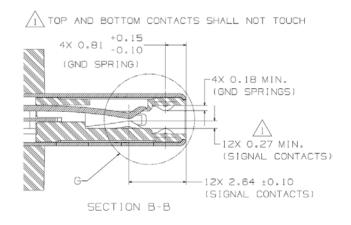

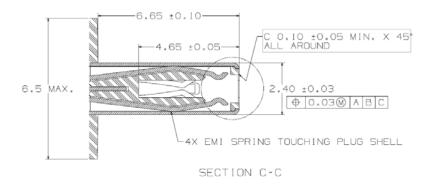

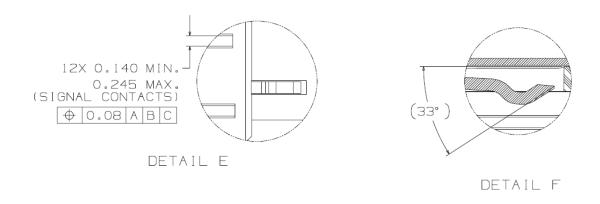

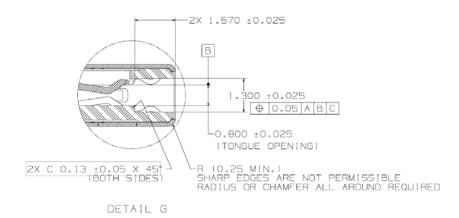

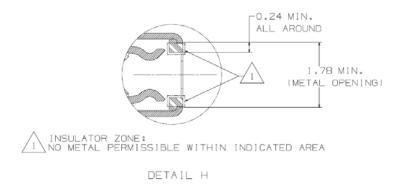

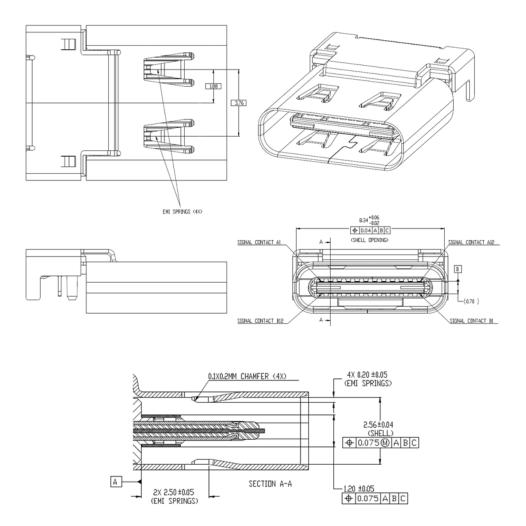

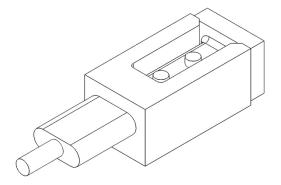

| Figure 3-2 | Referen   | ce Design USB Type-C Plug External EMC Spring Contact Zones                                | 34        |

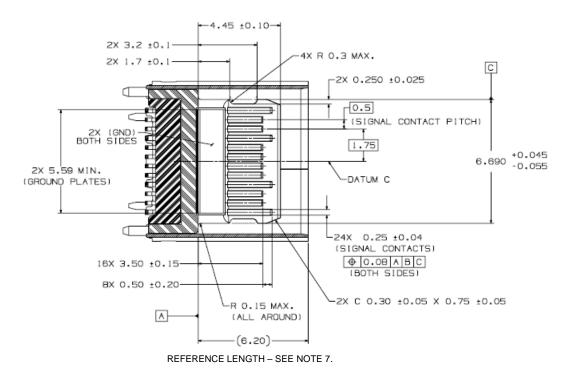

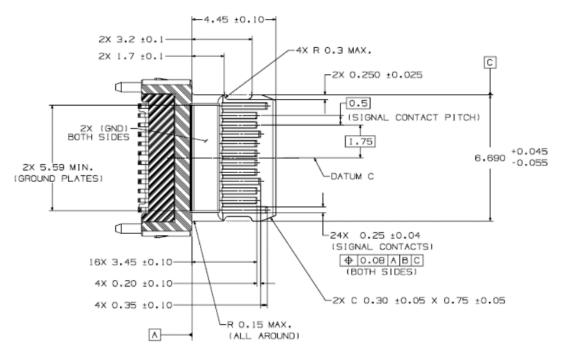

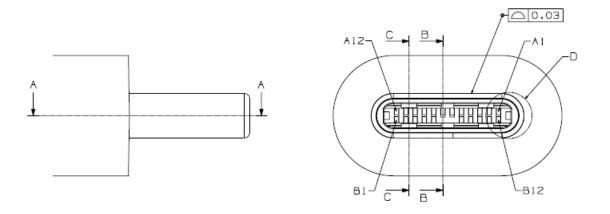

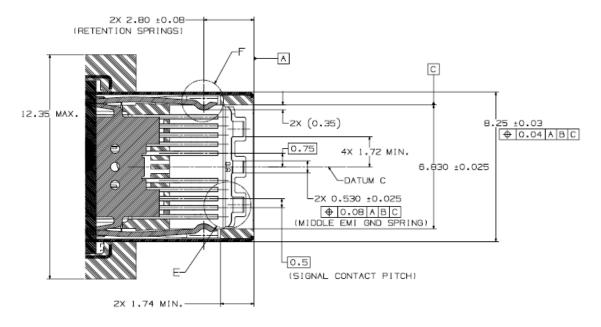

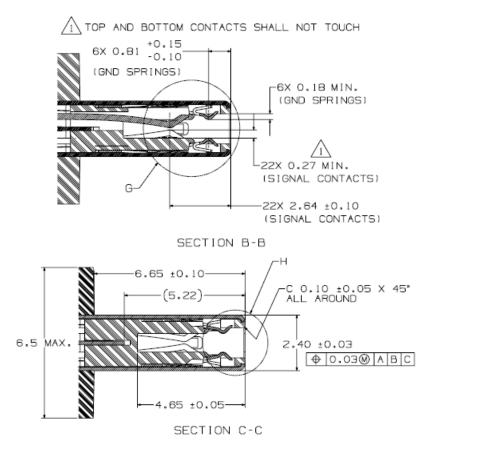

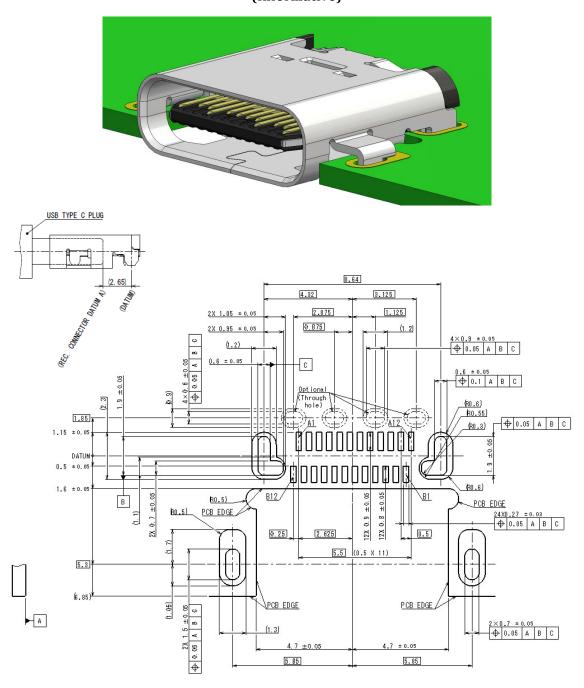

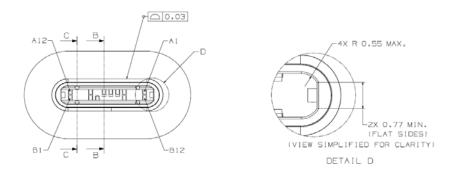

|            |           | ll-Featured Type-C Plug Interface Dimensions                                               |           |

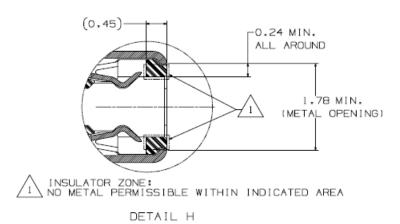

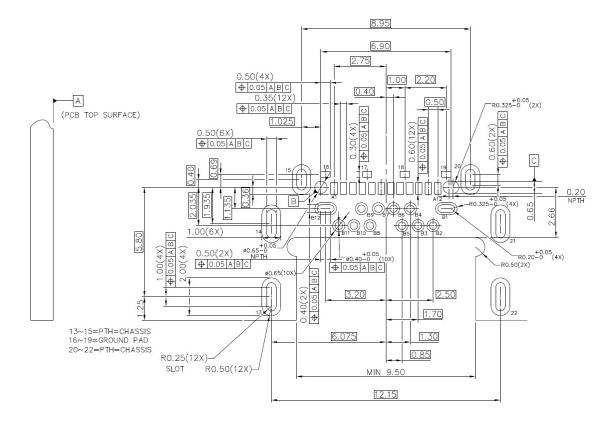

|            |           | ice Footprint for a USB Type-C Vertical Mount Receptacle (Informative                      | :)38      |

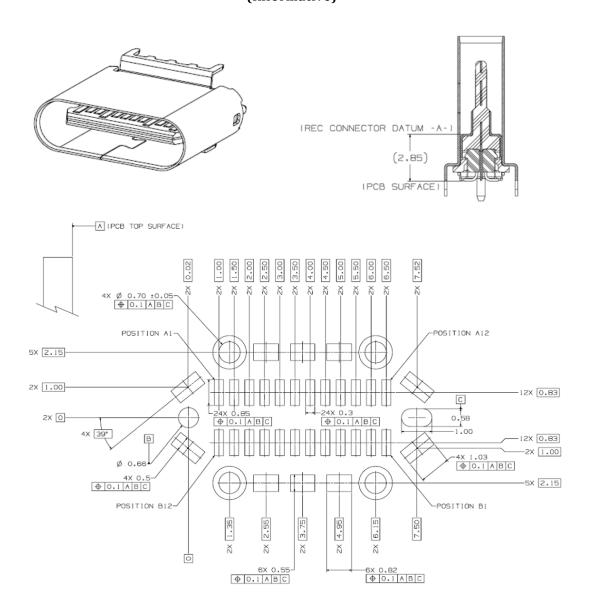

|            |           | ice Footprint for a USB Type-C Dual-Row SMT Right Angle Receptacle                         |           |

|            |           |                                                                                            |           |

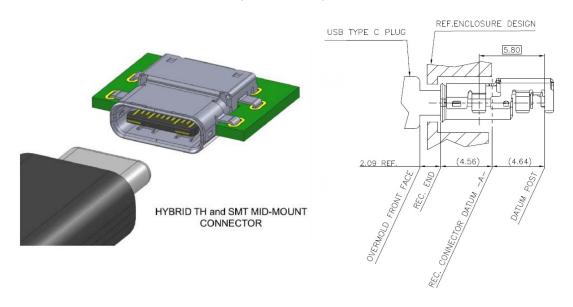

|            |           | ice Footprint for a USB Type-C Hybrid Right-Angle Receptacle (Inform                       | ative)40  |

|            |           | ice Footprint for a USB Type-C Mid-Mount Dual-Row SMT Receptacle                           |           |

|            |           |                                                                                            |           |

|            |           | ice Footprint for a USB Type-C Mid-Mount Hybrid Receptacle (Informa                        |           |

|            |           | Type-C Plug Interface Dimensions                                                           |           |

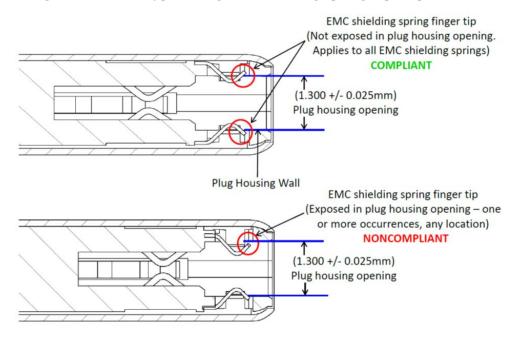

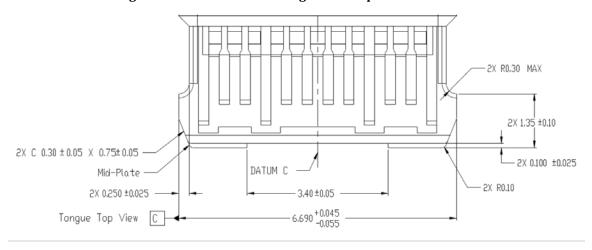

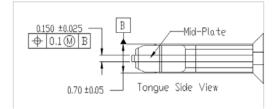

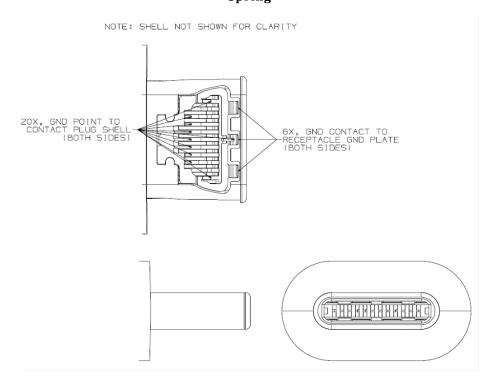

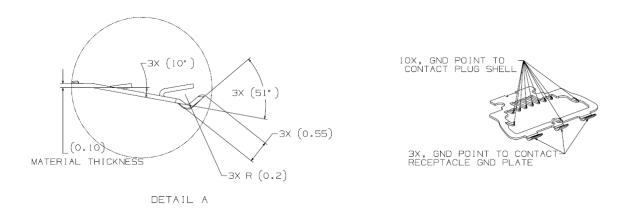

|            |           | ype-C Plug EMC Shielding Spring Tip Requirementsence Design of Receptacle Mid-Plate        |           |

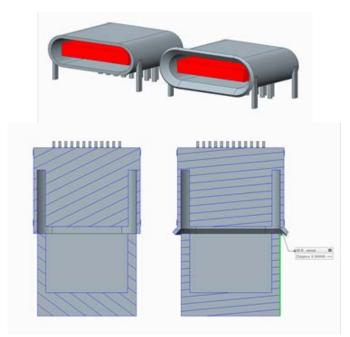

|            |           | ence Design of the Retention Latch                                                         |           |

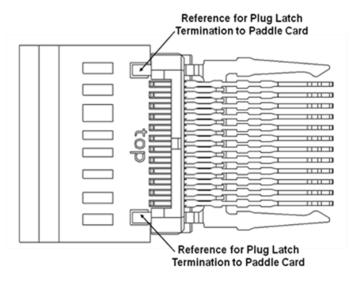

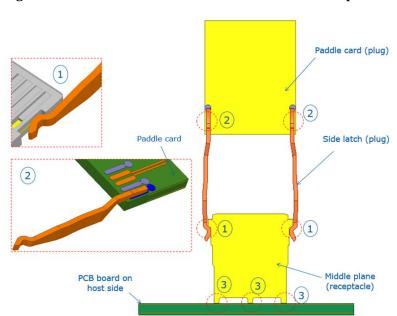

|            |           | ation of the Latch Soldered to the Paddle Card Ground                                      |           |

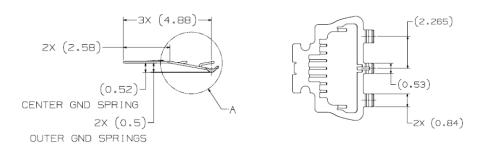

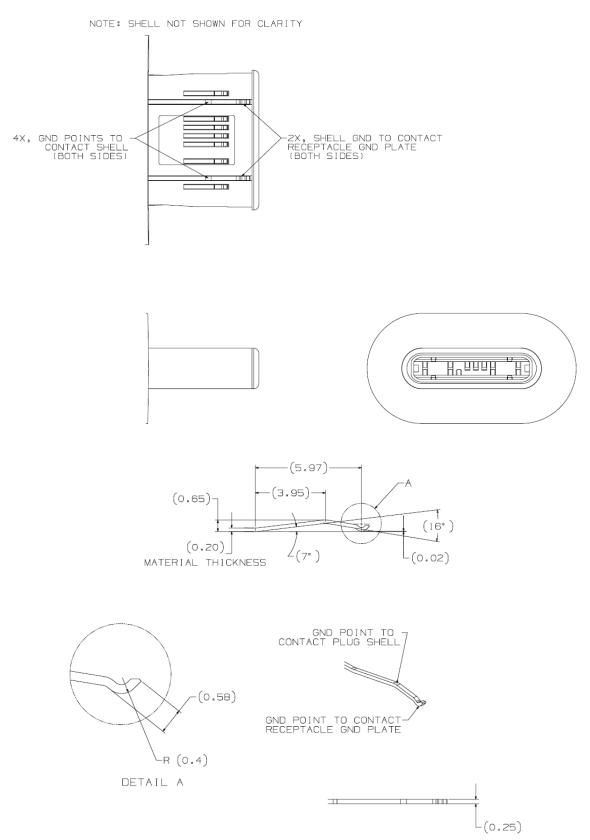

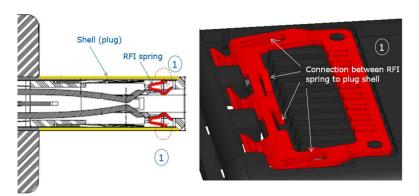

|            |           | ence Design of the USB Full-Featured Type-C Plug Internal EMC Spring                       |           |

|            |           | ence Design of the USB 2.0 Type-C Plug Internal EMC Spring                                 |           |

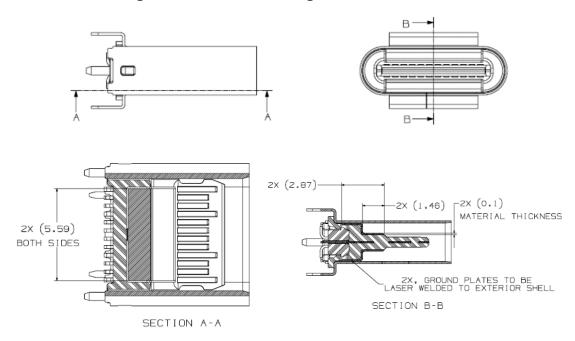

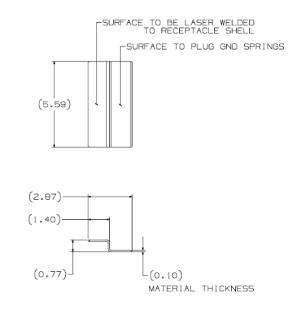

|            |           | ence Design of Internal EMC Pad                                                            |           |

|            |           | ence Design of a USB Type-C Receptacle with External EMC Springs                           |           |

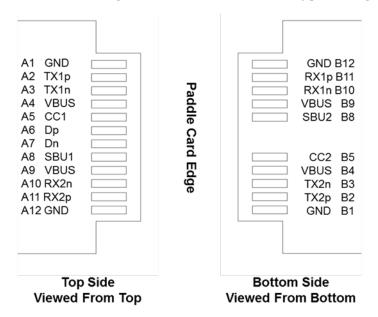

|            |           | ence Design for a USB Full-Featured Type-C Plug Paddle Card                                |           |

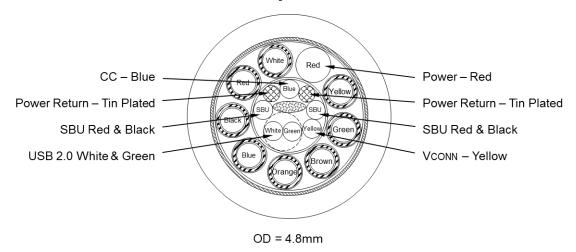

|            |           | ation of a USB Full-Featured Type-C Cable Cross Section, a Coaxial Wir                     |           |

| _          |           |                                                                                            | _         |

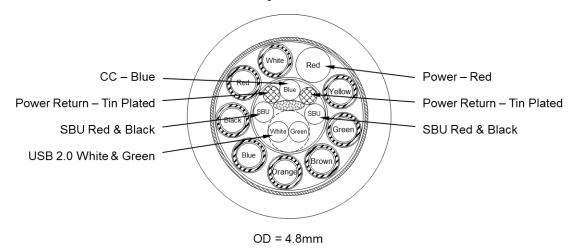

| Figure 3-2 | 0 Illustr | ation of a USB Full-Featured Type-C Cable Cross Section, a Coaxial Wir                     | e Example |

| witho      | ut Vconn  | I                                                                                          | 57        |

| Figure 3-2 | 1 USB Fi  | ull-Featured Type-C Standard Cable Assembly                                                | 61        |

|            |           | ype-C to USB 3.1 Standard-A Cable Assembly                                                 |           |

|            |           | ype-C to USB 2.0 Standard-A Cable Assembly                                                 |           |

|            |           | ype-C to USB 3.1 Standard-B Cable Assembly                                                 |           |

|            |           | ype-C to USB 2.0 Standard-B Cable Assembly                                                 |           |

|            |           | ype-C to USB 2.0 Mini-B Cable Assembly                                                     |           |

|            |           | ype-C to USB 3.1 Micro-B Cable Assembly                                                    |           |

|            |           | ype-C to USB 2.0 Micro-B Cable Assembly                                                    |           |

|            |           | ype-C to USB 3.1 Standard-A Receptacle Adapter Assembly                                    |           |

|            |           | ype-C to USB 2.0 Micro-B Receptacle Adapter Assembly                                       |           |

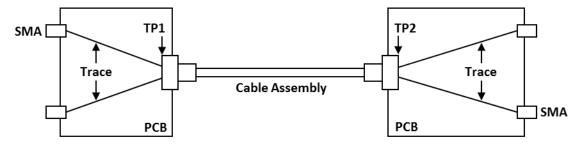

|            |           | ation of Test Points for a Mated Cable Assembly                                            |           |

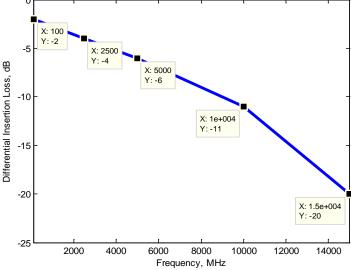

|            |           | nmended Differential Insertion Loss Requirement                                            |           |

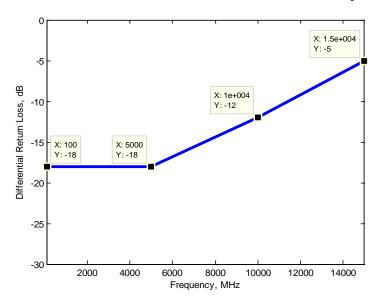

| _          |           | nmended Differential Return Loss Requirement<br>nmended Differential Crosstalk Requirement |           |

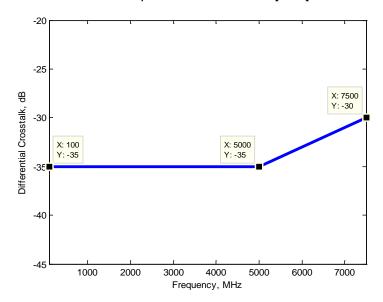

| rigure 3-3 | 4 кесот   | mengeg Differential Crossialk Keglifement                                                  |           |

|             | Recommended Differential Near-End and Far-End Crosstalk Requirement between  |          |

|-------------|------------------------------------------------------------------------------|----------|

|             | Pair and USB SuperSpeed Pair                                                 |          |

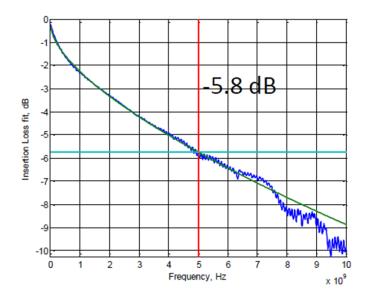

|             | Illustration of Insertion Loss Fit at Nyquist Frequency                      |          |

|             | Input Pulse Spectrum                                                         |          |

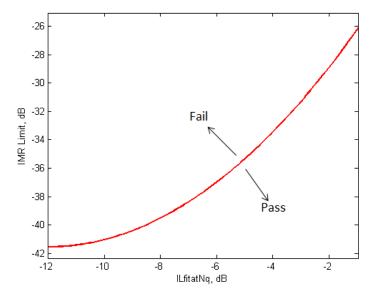

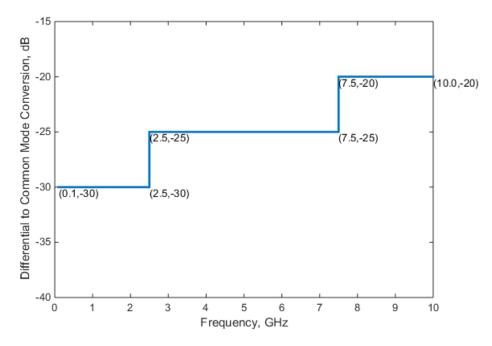

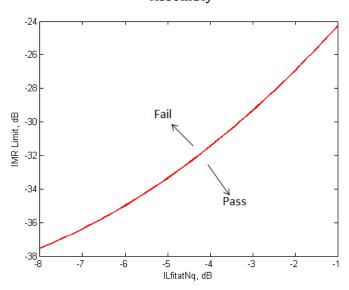

| Figure 3-38 | IMR Limit as Function of ILfitatNq                                           | 80       |

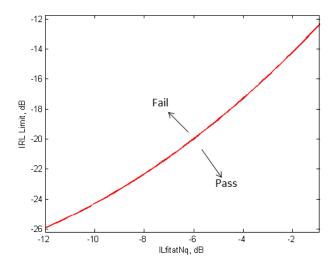

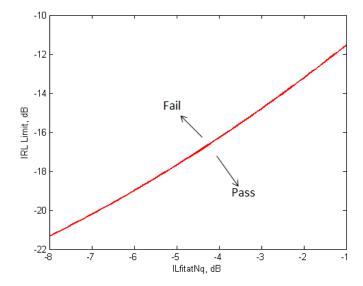

|             | IRL Limit as Function of ILfitatNq                                           |          |

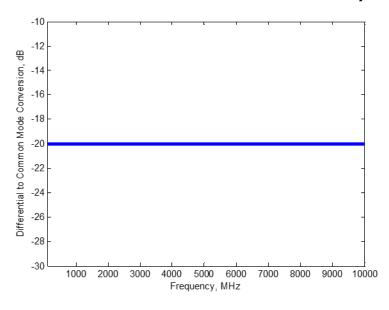

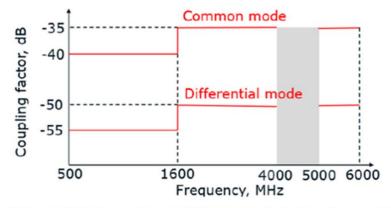

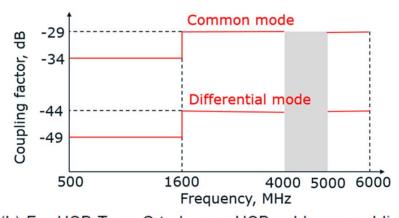

| Figure 3-40 | Differential-to-Common-Mode Conversion Requirement                           | 82       |

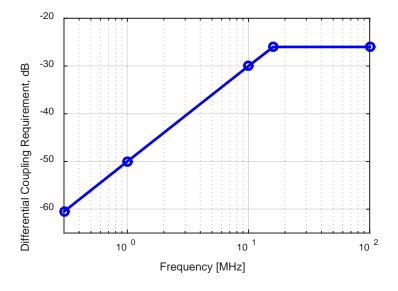

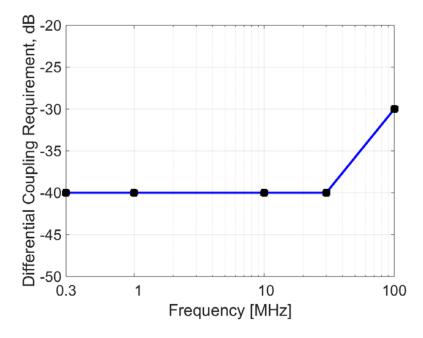

| Figure 3-41 | Requirement for Differential Coupling between CC and D+/D                    | 83       |

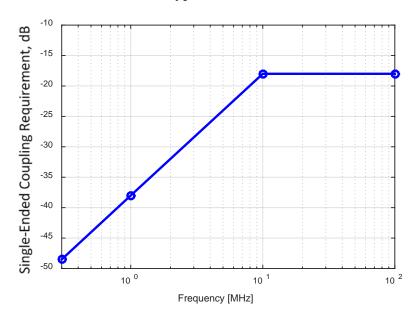

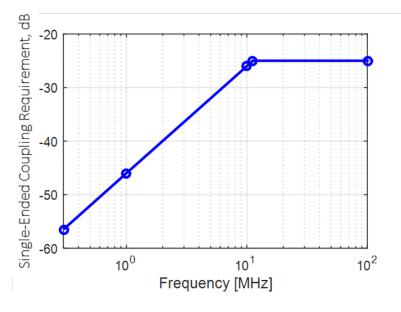

| Figure 3-42 | Requirement for Single-Ended Coupling between CC and D- in USB 2.0 Type-C Ca | ıbles.84 |

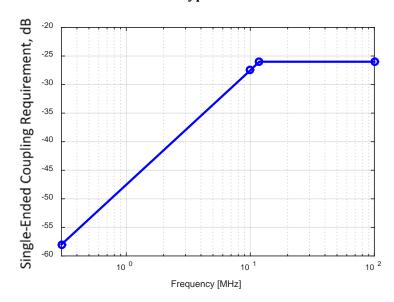

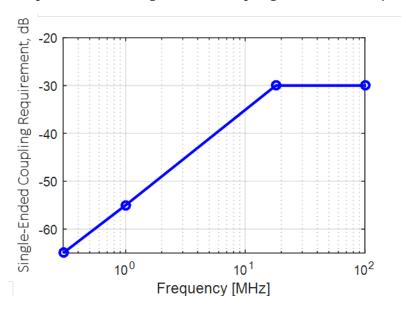

| Figure 3-43 | Requirement for Single-Ended Coupling between CC and D- in USB Full-Featured | Type-    |

|             | S                                                                            |          |

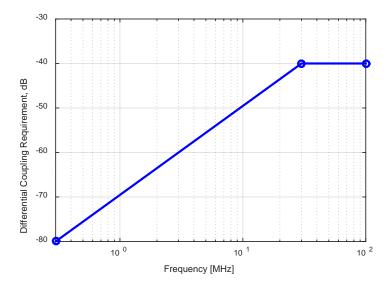

| Figure 3-44 | Requirement for Differential Coupling between VBUS and D+/D                  | 85       |

| Figure 3-45 | Requirement for Single-Ended Coupling between SBU_A and SBU_B                | 86       |

|             | Requirement for Single-Ended Coupling between SBU_A/SBU_B and CC             |          |

|             | Requirement for Coupling between SBU_A and differential D+/D-, and SBU_B and |          |

|             | ntial D+/D                                                                   |          |

|             | Illustration of USB Type-C Mated Connector                                   |          |

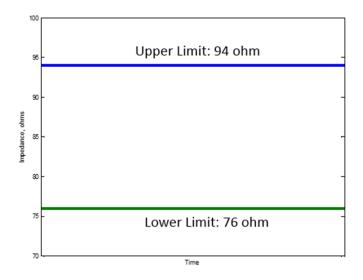

|             | Recommended Impedance Limits of a USB Type-C Mated Connector                 |          |

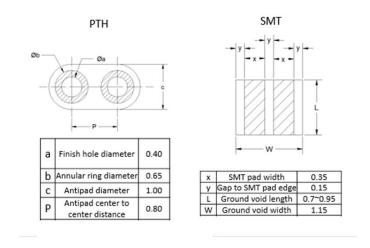

|             | Recommended Ground Void Dimensions for USB Type-C Receptacle                 |          |

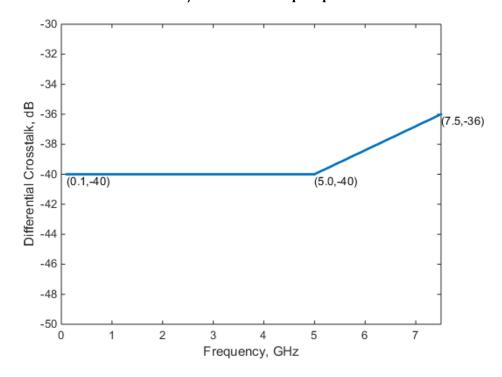

|             | Recommended Differential Near-End and Far-End Crosstalk Limits between D+/I  |          |

|             | perSpeed Pairs                                                               |          |

|             | Recommended Limits for Differential-to-Common-Mode Conversion                |          |

|             | IMR Limit as Function of ILfitatNq for USB Type-C to Legacy Cable Assembly   |          |

|             | IRL Limit as Function of ILlitatNq for USB Type-C to Legacy Cable Assembly   |          |

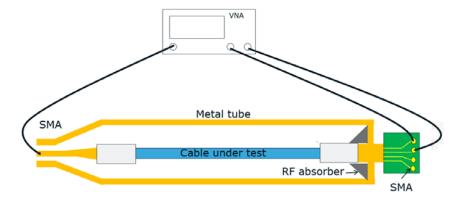

|             | Cable Assembly Shielding Effectiveness Testing                               |          |

|             | Shielding Effectiveness Pass/Fail Criteria                                   |          |

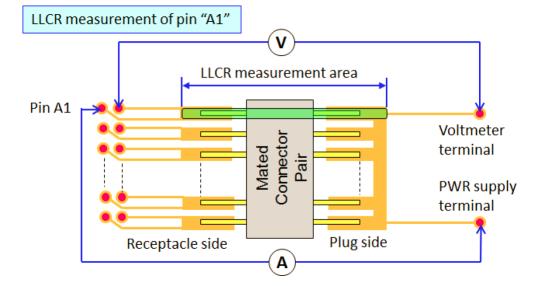

|             | LLCR Measurement Diagram                                                     |          |

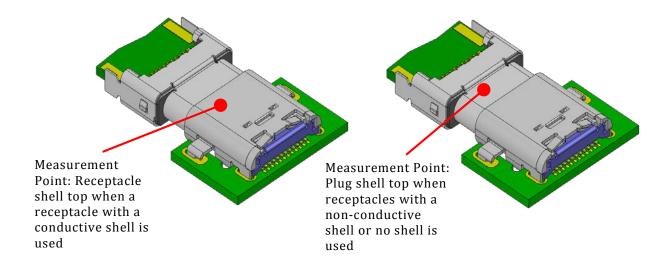

| 0           | Temperature Measurement Point                                                |          |

|             | Example Current Rating Test Fixture Trace Configuration                      |          |

|             | Example of 4-Axis Continuity Test Fixture                                    |          |

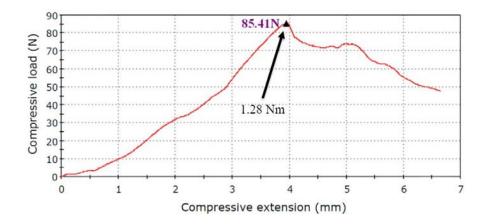

|             | Example Wrenching Strength Test Fixture for Plugs without Overmold           |          |

|             | Reference Wrenching Strength Continuity Test Fixture                         |          |

|             | Example of Wrenching Strength Test Mechanical Failure Point                  |          |

|             | Wrenching Strength Test with Cable in Fixture                                |          |

|             | USB Type-C Cable Receptacle Flange Example                                   |          |

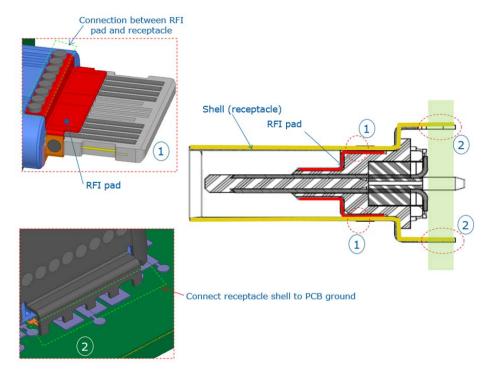

| 0           | EMC Guidelines for Side Latch and Mid-plate                                  |          |

|             | EMC Finger Connections to Plug Shell                                         |          |

|             | EMC Pad Connections to Pidg Shell                                            |          |

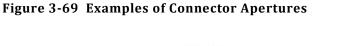

|             | Examples of Connector Apertures                                              |          |

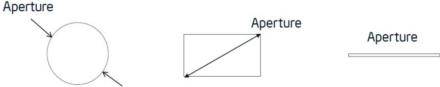

|             | Recommended Minimum Spacing between Connectors                               |          |

| _           |                                                                              |          |

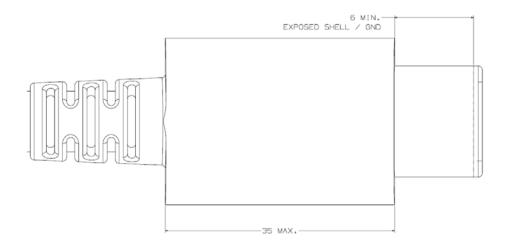

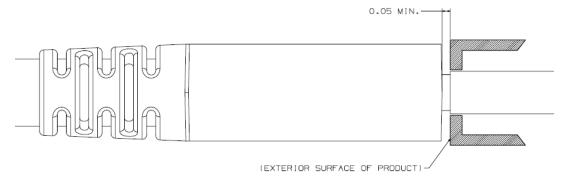

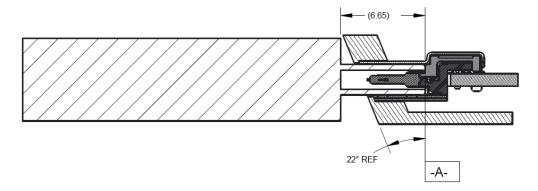

|             | Recommended Minimum Plug Overmold Clearance                                  |          |

| _           | Cable Plug Overmold and an Angled Surface                                    |          |

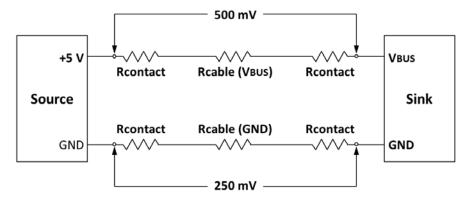

|             | Cable IR Drop                                                                |          |

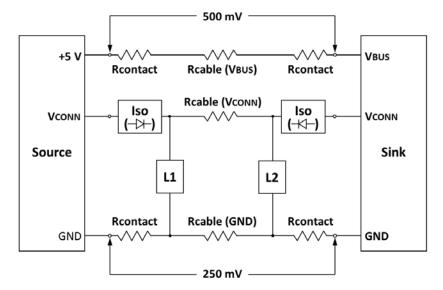

|             | Cable IR Drop for powered cables                                             |          |

|             | Logical Model for Data Bus Routing across USB Type-C-based Ports             |          |

|             | Logical Model for USB Type-C-based Ports for the Direct Connect Device       |          |

| 0           | Pull-Up/Pull-Down CC Model                                                   |          |

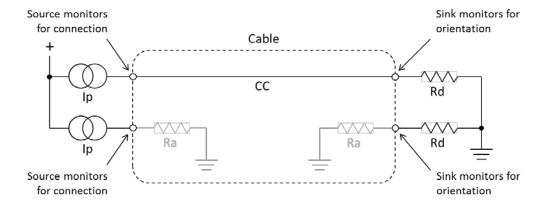

|             | Current Source/Pull-Down CC Model                                            |          |

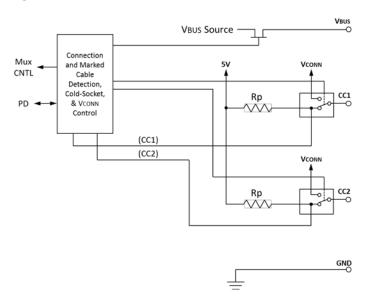

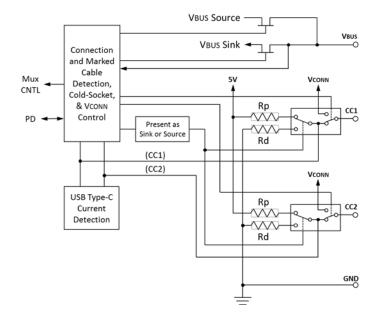

|             | Source Functional Model for CC1 and CC2                                      |          |

| _           | Source Functional Model Supporting USB PD PR_Swap                            |          |

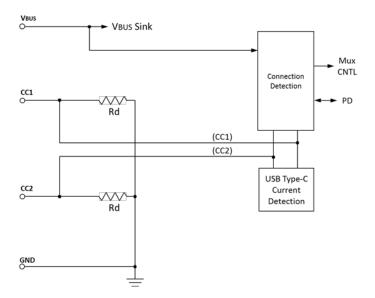

| 0           | Sink Functional Model for CC1 and CC2                                        |          |

|             | UFP Functional Model Supporting USB PD PR_Swap and VCONN_Swap                |          |

| 0           | DRP Functional Model for CC1 and CC2                                         |          |

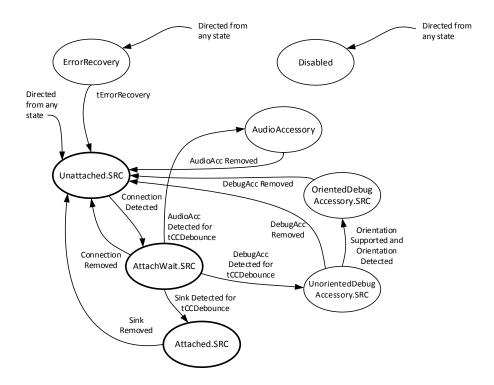

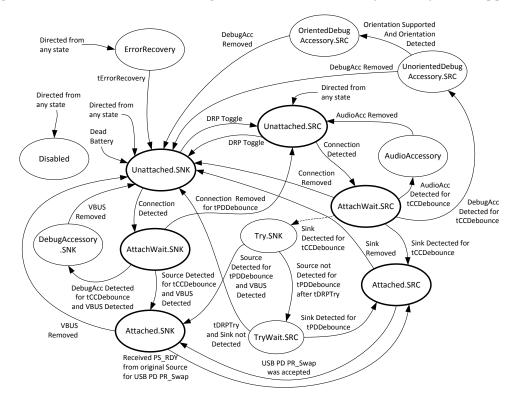

| _           | Connection State Diagram: Source                                             |          |

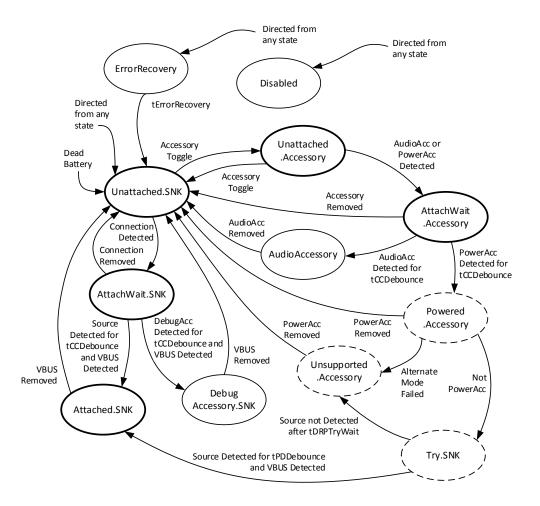

| Figure 4-13 | Connection State Diagram: Sink                                               | 135      |

| Figure 4-14 Connection State Diagram: Sink with Accessory Support                          | 136 |

|--------------------------------------------------------------------------------------------|-----|

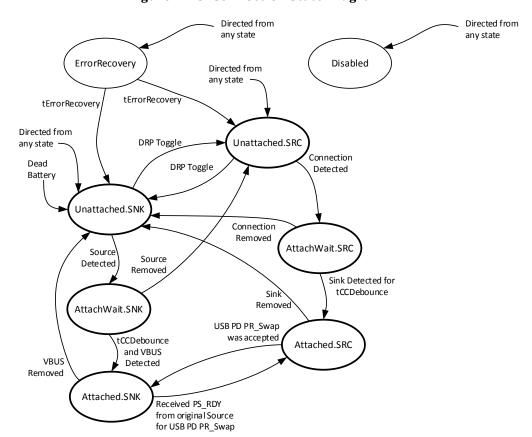

| Figure 4-15 Connection State Diagram: DRPDRP                                               |     |

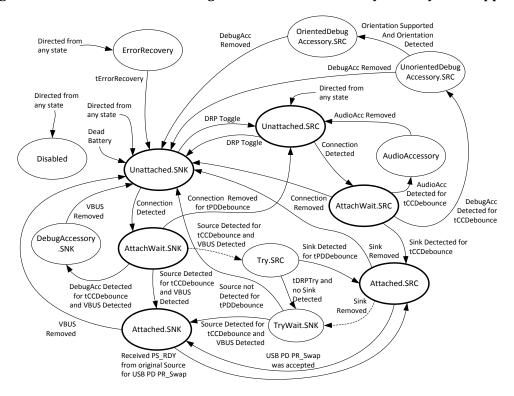

| Figure 4-16 Connection State Diagram: DRP with Accessory and Try.SRC Support               | 138 |

| Figure 4-17 Connection State Diagram: DRP with Accessory and Try.SNK Support               | 139 |

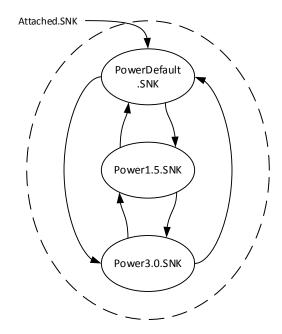

| Figure 4-18 Sink Power Sub-States                                                          |     |

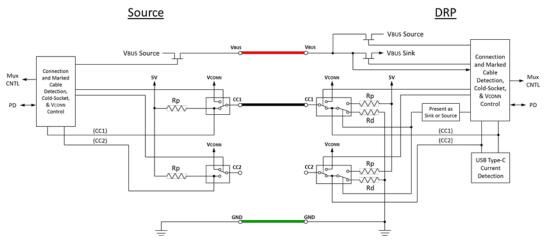

| Figure 4-19 Source to Sink Functional Model                                                |     |

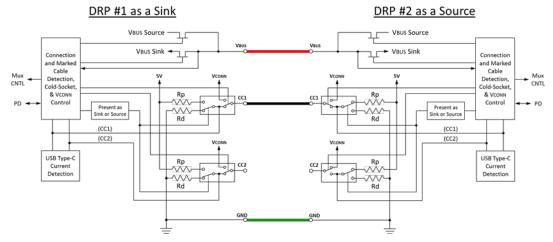

| Figure 4-20 Source to DRP Functional Model                                                 | 156 |

| Figure 4-21 DRP to Sink Functional Model                                                   |     |

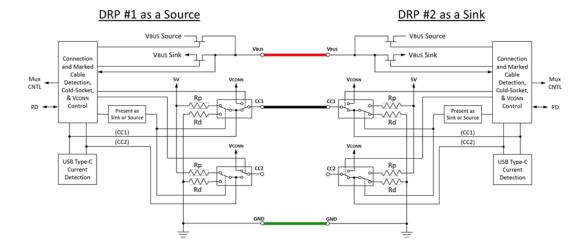

| Figure 4-22 DRP to DRP Functional Model – CASE 1                                           |     |

| Figure 4-23 DRP to DRP Functional Model – CASE 2 & 3                                       |     |

| Figure 4-24 Source to Source Functional Model                                              |     |

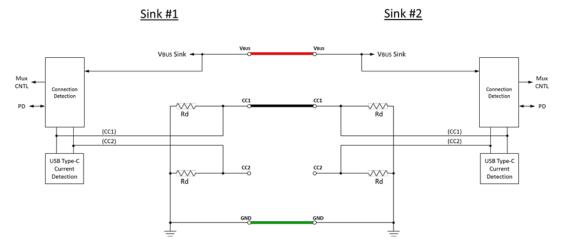

| Figure 4-25 Sink to Sink Functional Model                                                  |     |

| Figure 4-26 Source to Legacy Device Port Functional Model                                  |     |

| Figure 4-27 Legacy Host Port to Sink Functional Model                                      |     |

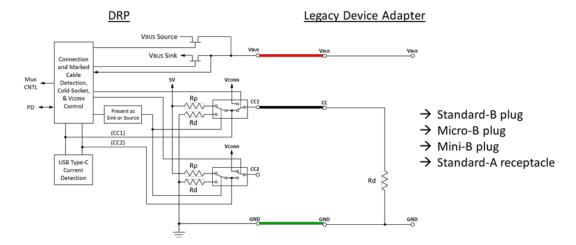

| Figure 4-28 DRP to Legacy Device Port Functional Model                                     |     |

| Figure 4-29 Legacy Host Port to DRP Functional Model                                       |     |

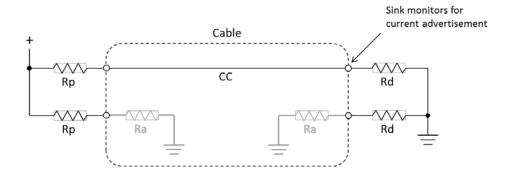

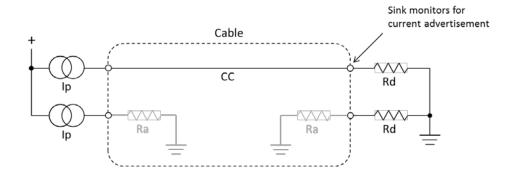

| Figure 4-30 Sink Monitoring for Current in Pull-Up/Pull-Down CC Model                      |     |

| Figure 4-31 Sink Monitoring for Current in Current Source/Pull-Down CC Model               |     |

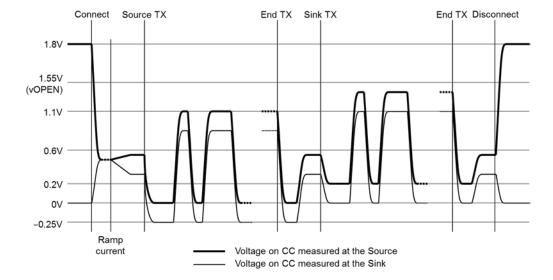

| Figure 4-32 USB PD over CC Pins                                                            |     |

| Figure 4-33 USB PD BMC Signaling over CC                                                   | 170 |

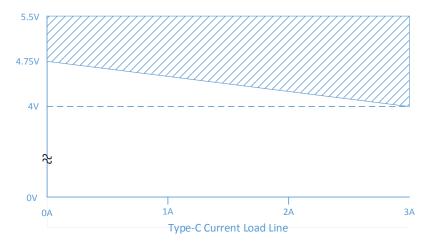

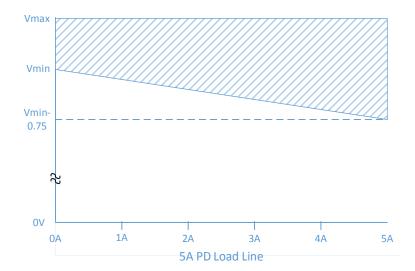

| Figure 4-34 USB Type-C Cable's Output as a Function of Load for Non-PD-based USB Type-C    |     |

| Charging                                                                                   | 172 |

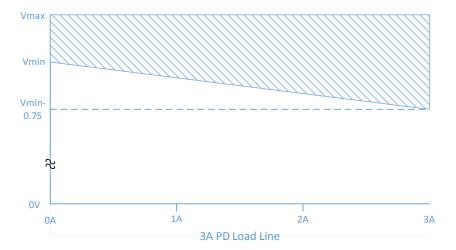

| Figure 4-35 0 – 3 A USB PD-based Charger USB Type-C Cable's Output as a Function of Load   |     |

| Figure 4-36 3 – 5 A USB PD-based Charger USB Type-C Cable's Output as a Function of Load   |     |

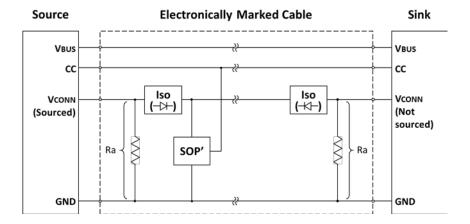

| Figure 4-37 Electronically Marked Cable with VCONN connected through the cable             |     |

| Figure 4-38 Electronically Marked Cable with SOP' at both ends                             |     |

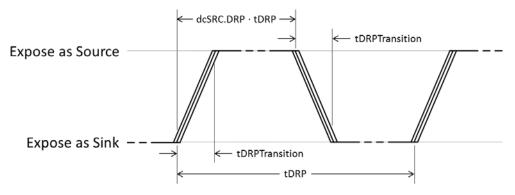

| Figure 4-39 DRP Timing                                                                     |     |

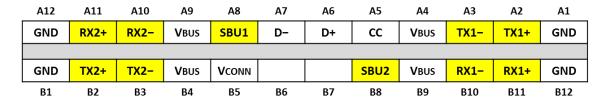

| Figure 5-1 Pins Available for Reconfiguration over the Full-Featured Cable                 |     |

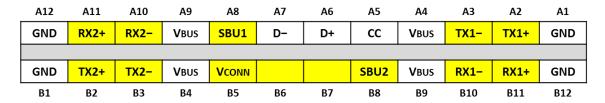

| Figure 5-2 Pins Available for Reconfiguration for Direct Connect Applications              |     |

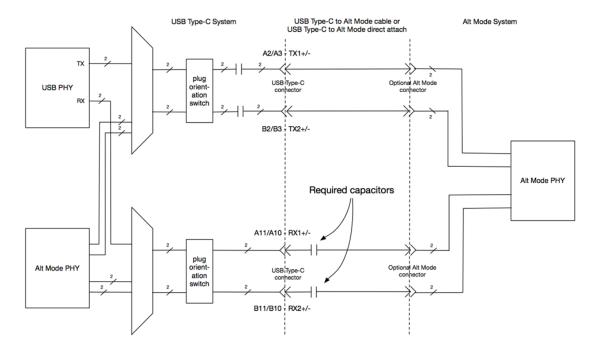

| Figure 5-3 Alternate Mode Implementation using a USB Type-C to USB Type-C Cable            |     |

| Figure 5-4 Alternate Mode Implementation using a USB Type-C to Alternate Mode Cable or Dev |     |

|                                                                                            |     |

| Figure 5-5 USB DisplayPort Dock Example                                                    | 188 |

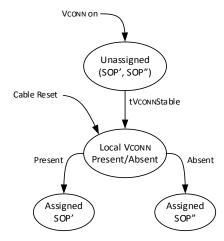

| Figure 5-6 Managed Active Cable Plug SOP' and SOP" Assignment                              | 191 |

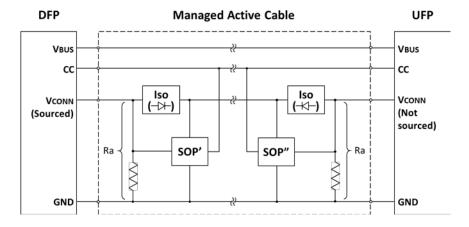

| Figure 5-7 Managed Active Cable                                                            |     |

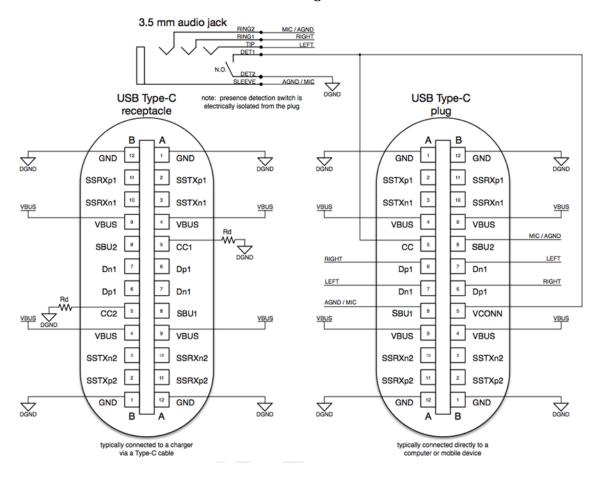

| Figure A-1 Example Passive 3.5 mm to USB Type-C Adapter                                    | 197 |

| Figure A-2 Example 3.5 mm to USB Type-C Adapter Supporting 500 mA Charge-Through           |     |

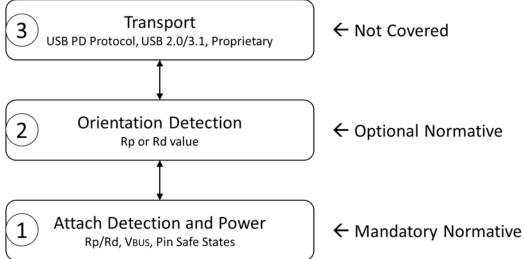

| Figure B-1 USB Type-C Debug Accessory Layered Behavior                                     |     |

| Figure B-2 DTS Plug Interface                                                              |     |

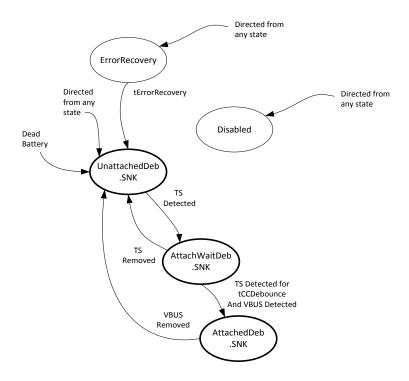

| Figure B-3 Connection State Diagram: DTS Source                                            |     |

| Figure B-4 Connection State Diagram: DTS Sink                                              |     |

| Figure B-5 Connection State Diagram: DTS DRP                                               |     |

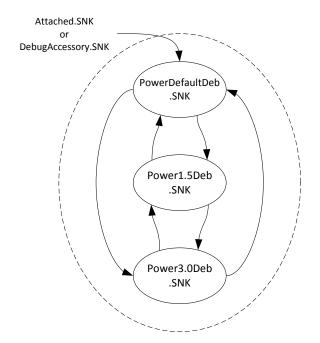

| Figure B-6 TS Sink Power Sub-States                                                        |     |

|                                                                                            |     |

| TABLES                                                                                     |     |

| Table 2-1 Summary of power supply options                                                  |     |

| Table 3-1 USB Type-C Standard Cable Assemblies                                             |     |

| Table 3-2 USB Type-C Legacy Cable Assemblies                                               | 28  |

| Table 3-3 USB Type-C Legacy Adapter Assemblies                                             |     |

| Table 3-4 USB Type-C Receptacle Interface Pin Assignments                                  |     |

| Table 3-5 USB Type-C Receptacle Interface Pin Assignments for USB 2.0-only Support         | 56  |

| Table 3-6 USB Type-C Standard Cable Wire Assignments                                       |     |

| Table 3-7 USB Type-C Cable Wire Assignments for Legacy Cables/Adapters                     | 59  |

| Table 3-8 Reference Wire Gauges for standard USB Type-C Cable Assemblies                            | 60  |

|-----------------------------------------------------------------------------------------------------|-----|

| Table 3-9 Reference Wire Gauges for USB Type-C to Legacy Cable Assemblies                           |     |

| Table 3-10 USB Full-Featured Type-C Standard Cable Assembly Wiring                                  | 62  |

| Table 3-11 USB 2.0 Type-C Standard Cable Assembly Wiring                                            | 63  |

| Table 3-12 USB Type-C to USB 3.1 Standard-A Cable Assembly Wiring                                   |     |

| Table 3-13 USB Type-C to USB 2.0 Standard-A Cable Assembly Wiring                                   |     |

| Table 3-14 USB Type-C to USB 3.1 Standard-B Cable Assembly Wiring                                   |     |

| Table 3-15 USB Type-C to USB 2.0 Standard-B Cable Assembly Wiring                                   |     |

| Table 3-16 USB Type-C to USB 2.0 Mini-B Cable Assembly Wiring                                       |     |

| Table 3-17 USB Type-C to USB 3.1 Micro-B Cable Assembly Wiring                                      |     |

| Table 3-18 USB Type-C to USB 2.0 Micro-B Cable Assembly Wiring                                      |     |

| Table 3-19 USB Type-C to USB 3.1 Standard-A Receptacle Adapter Assembly Wiring                      |     |

| Table 3-20 USB Type-C to USB 2.0 Micro-B Receptacle Adapter Assembly Wiring                         |     |

| Table 3-21 Differential Insertion Loss Examples for USB SuperSpeed with Twisted Pair Constru        |     |

|                                                                                                     |     |

| Table 3-22 Differential Insertion Loss Examples for USB SuperSpeed with Coaxial Construction.       |     |

| Table 3-23 Electrical Requirements for CC and SBU wires                                             |     |

| Table 3-24 Coupling Matrix for Low Speed Signals                                                    |     |

| Table 3-24 USB D+/D- Signal Integrity Requirements for USB Type-C to USB Type-C Passive Ca          |     |

| Assemblies                                                                                          |     |

| Table 3-25 USB Type-C Mated Connector Recommended Signal Integrity Characteristics                  |     |

| (Informative)                                                                                       | 89  |

| Table 3-26 USB D+/D- Signal Integrity Requirements for USB Type-C to Legacy USB Cable               |     |

| Assemblies                                                                                          | 92  |

| Table 3-27 Design Targets for USB Type-C to <i>USB 3.1</i> Gen 2 Legacy Cable Assemblies (Informati |     |

| Table 3-28 USB Type-C to <i>USB 3.1</i> Gen 2 Legacy Cable Assembly Signal Integrity Requirements   | ,   |

| (Normative)                                                                                         | 93  |

| Table 3-29 USB D+/D- Signal Integrity Requirements for USB Type-C to Legacy USB Adapter             |     |

| Assemblies (Normative)                                                                              | 95  |

| Table 3-30 Design Targets for USB Type-C to USB 3.1 Standard-A Adapter Assemblies (Informat         |     |

| ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,                                                              |     |

| Table 3-31 USB Type-C to USB 3.1 Standard-A Receptacle Adapter Assembly Signal Integrity            |     |

| Requirements (Normative)                                                                            | 97  |

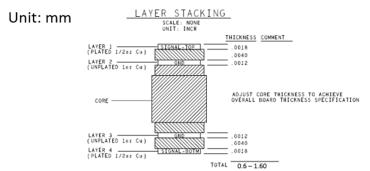

| Table 3-32 Current Rating Test PCB                                                                  |     |

| Table 3-33 Force and Moment Requirements                                                            |     |

| Table 3-34 Environmental Test Conditions                                                            |     |

| Table 3-35 Reference Materials                                                                      |     |

| Table 4-1 USB Type-C List of Signals                                                                |     |

| Table 4-2 VBUS Source Characteristics                                                               |     |

| Table 4-3 USB Type-C Source Port's VCONN Requirements Summary                                       |     |

| Table 4-4 VCONN Source Characteristics                                                              |     |

| Table 4-5 VCONN Sink Characteristics                                                                |     |

| Table 4-6 USB Type-C-based Port Interoperability                                                    |     |

| Table 4-7 Source Perspective                                                                        |     |

| Table 4-8 Source (Host) and Sink (Device) Behaviors by State                                        |     |

| Table 4-9 USB PD Swapping Port Behavior Summary                                                     |     |

| Table 4-10 Power Role Behavioral Model Summary                                                      |     |

| Table 4-11 Source Port CC Pin State                                                                 |     |

| Table 4-12 Sink Port CC Pin State                                                                   |     |

| Table 4-13 Mandatory and Optional States                                                            |     |

| Table 4-14 Precedence of power source usage                                                         |     |

| Table 4-15 Source CC Termination (Rp) Requirements                                                  |     |

| Table 4-16 Sink CC Termination (Rd) Requirements                                                    |     |

| Table 4-17 Powered Cable Termination Requirements                                                   |     |

| Table 4-18 Sink CC Termination Requirements                                                         | 178 |

| Table 4-19        | SBU Termination Requirements                                                   | 178  |

|-------------------|--------------------------------------------------------------------------------|------|

| <b>Table 4-20</b> | VBUS and VCONN Timing Parameters                                               | .179 |

| Table 4-21        | DRP Timing Parameters                                                          | 180  |

| Table 4-22        | DRP Timing Parameters                                                          | 181  |

| Table 4-23        | CC Voltages on Source Side – Default USB                                       | .181 |

| Table 4-24        | CC Voltages on Source Side – 1.5 A @ 5 V                                       | .181 |

|                   | 6 CC Voltages on Source Side - 3.0 A @ 5 V                                     |      |

| Table 4-26        | Voltage on Sink CC Pins (Default USB Type-C Current only)                      | .182 |

| <b>Table 4-27</b> | Voltage on Sink CC pins (Multiple Source Current Advertisements)               | .182 |

| Table 5-1         | USB Safe State Electrical Requirements                                         | .187 |

| Table 5-2         | USB Billboard Device Class Availability Following Alternate Mode Entry Failure | .187 |

| Table 5-3         | Alternate Mode Signal Noise Ingression Requirements                            | 187  |

| Table 5-4         | SOP' and SOP" Timing                                                           | 192  |

| Table A-1         | USB Type-C Analog Audio Pin Assignments                                        | 195  |

| Table A-2         | USB Type-C Analog Audio Pin Electrical Parameter Ratings                       | .196 |

| Table B-1         | DTS to TS Port Interoperability                                                | 200  |

| Table B-2         | DTS to TS Port Interoperability                                                | .208 |

|                   | Mandatory and Optional States                                                  |      |

#### Specification Work Group Chairs / Specification Editors

Intel Corporation (USB 3.0 Promoter company) Yun Ling – Mechanical WG co-chair, Mechanical Chapter Co-editor Bob Dunstan – Functional WG co-chair, Specification Co-author Brad Saunders – Plenary/Functional WG chair, Specification Co-author

Seagate Alvin Cox, Mechanical WG co-chair, Mechanical Chapter Co-editor

#### **Specification Work Group Contributors**

| Advanced-Connectek, Inc.<br>(ACON)                | Glen Chandler<br>Jeff Chien<br>Lee (Dick Lee) Ching<br>Conrad Choy                                                 | Vicky Chuang<br>Aven Kao<br>Danny Liao<br>Alan MacDougall                                        | Alan Tsai<br>Stephen Yang                                                                 |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

| Advanced Micro Devices                            | Steve Capezza                                                                                                      | Walter Fry                                                                                       | Will Harris                                                                               |

| Agilent Technologies, Inc.                        | James Choate                                                                                                       |                                                                                                  |                                                                                           |

| Analogix Semiconductor, Inc.                      | Mehran Badii                                                                                                       | Greg Stewart                                                                                     |                                                                                           |

| Apple                                             | Mahmoud Amini<br>Sree Anantharaman<br>Paul Baker<br>Jason Chung<br>David Conroy<br>Bill Cornelius<br>William Ferry | Zheng Gao<br>Girault Jones<br>Keong Kam<br>Min Kim<br>Chris Ligtenberg<br>Nathan Ng<br>James Orr | Keith Porthouse<br>Sascha Tietz<br>Jennifer Tsai<br>Colin Whitby-Strevens<br>Dennis Yarak |

| Cypress Semiconductor                             | Mark Fu<br>Rushil Kadakia                                                                                          | Anup Nayak<br>Jagadeesan Raj                                                                     | Sanjay Sancheti<br>Subu Sankaran                                                          |

| Dell                                              | Mohammed Hijazi<br>David Meyers                                                                                    | Sean O'Neal<br>Ernesto Ramirez                                                                   | Thomas Voor                                                                               |

| DisplayLink (UK) Ltd.                             | Pete Burgers                                                                                                       | Richard Petrie                                                                                   |                                                                                           |

| Electronics Testing Center,<br>Taiwan             | Sophia Liu                                                                                                         |                                                                                                  |                                                                                           |

| Foxconn                                           | Asroc Chen<br>Allen Cheng<br>Jason Chou<br>Edmond Choy<br>Bob Hall                                                 | Chien-Ping Kao<br>Ji Li<br>Ann Liu<br>Terry Little<br>Steve Sedio                                | Pei Tsao<br>AJ Yang<br>Yuan Zhang<br>Jessica Zheng<br>Andy Yao                            |

| Foxlink/Cheng Uei Precision<br>Industry Co., Ltd. | Robert Chen<br>Sunny Chou<br>Carrie Chuang<br>Wen-Chuan Hsu<br>Alex Hsue                                           | Armando Lee<br>Dennis Lee<br>Justin Lin<br>Tse Wu Ting                                           | Steve Tsai<br>Wen Yang<br>Wiley Yang<br>Junjie Yu                                         |

| Google                                            | Joshua Boilard<br>Alec Berg<br>Todd Broch<br>Jim Guerin<br>Jeffrey Hayashida                                       | Mark Hayter<br>Nithya Jagannathan<br>Lawrence Lam<br>Ingrid Lin<br>Richard Palatin               | Adam Rodriguez<br>David Schneider<br>Ken Wu                                               |

| Granite River Labs                                | Mike Engbretson                                                                                                    | Johnson Tan                                                                                      |                                                                                           |

| Hewlett Packard<br>(USB 3.0 Promoter<br>company)  | Alan Berkema<br>Robin Castell                                                                                      | Michael Krause<br>Jim Mann                                                                       | Linden McClure<br>Mike Pescetto                                                           |

| Hirose Electric Co., Ltd.                                  | Jeremy Buan<br>William MacKillop                                                                                        | Gourgen Oganessyan                                                                                                               | Sid Tono                                                                                                                   |

|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| Intel Corporation<br>(USB 3.0 Promoter<br>company)         | Dave Ackelson Mike Bell Kuan-Yu Chen Hengju Cheng Bob Dunstan Paul Durley Howard Heck Hao-Han Hsu Abdul (Rahman) Ismail | James Jaussi Luke Johnson Jerzy Kolinski Rolf Kuhnis Christine Krause Henrik Leegaard Yun Ling Xiang Li Guobin Liu Steve McGowan | Sankaran Menon Chee Lim Nge Sridharan Ranganathan Brad Saunders Amit Srivastava Ron Swartz Karthi Vadivelu Rafal Wielicki  |

| Japan Aviation Electronics<br>Industry Ltd. (JAE)          | Kenji Hagiwara<br>Masaki Kimura<br>Toshio Masumoto<br>Joe Motojima<br>Ron Muir<br>Tadashi Okubo<br>Kazuhiro Saito       | Kimiaki Saito<br>Yuichi Saito<br>Mark Saubert<br>Toshio Shimoyama<br>Tatsuya Shioda<br>Atsuo Tago<br>Masaaki Takaku              | Jussi Takaneva<br>Tomohiko Tamada<br>Kentaro Toda<br>Kouhei Ueda<br>Takakazu Usami<br>Masahide Watanabe<br>Youhei Yokoyama |

| JPC/Main Super Inc.                                        | Sam Tseng                                                                                                               | Ray Yang                                                                                                                         |                                                                                                                            |

| LeCroy Corporation                                         | Daniel H. Jacobs                                                                                                        |                                                                                                                                  |                                                                                                                            |

| Lenovo                                                     | Rob Bowser<br>Tomoki Harada                                                                                             | Wei Liu                                                                                                                          | Howard Locker                                                                                                              |

| Lotes Co., Ltd.                                            | Ariel Delos Reyes<br>Ernest Han<br>Mark Ho                                                                              | Regina Liu-Hwang<br>Max Lo<br>Charles Kaun                                                                                       | JinYi Tu<br>Jason Yang                                                                                                     |

| LSI Corporation                                            | Dave Thompson                                                                                                           |                                                                                                                                  |                                                                                                                            |

| Luxshare-ICT                                               | Josue Castillo<br>Daniel Chen<br>Lisen Chen                                                                             | CY Hsu<br>Alan Kinningham<br>John Lin                                                                                            | Stone Lin<br>Pat Young                                                                                                     |

| MegaChips Corporation                                      | Alan Kobayashi                                                                                                          |                                                                                                                                  |                                                                                                                            |

| Microchip (SMSC)                                           | Josh Averyt<br>Mark Bohm                                                                                                | Donald Perkins                                                                                                                   | Mohammed Rahman                                                                                                            |

| Microsoft Corporation<br>(USB 3.0 Promoter<br>company)     | Randy Aull<br>Fred Bhesania<br>Anthony Chen<br>Marty Evans<br>Vivek Gupta<br>Robbie Harris                              | Robert Hollyer<br>Kai Inha<br>Jayson Kastens<br>Andrea Keating<br>Eric Lee                                                       | Ivan McCracken<br>Toby Nixon<br>Gene Obie<br>Srivatsan Ravindran<br>David Voth                                             |

| MQP Electronics Ltd.                                       | Sten Carlsen                                                                                                            | Pat Crowe                                                                                                                        |                                                                                                                            |

| Nokia Corporation                                          | Daniel Gratiot<br>Pekka Leinonen                                                                                        | Samuli Makinen<br>Pekka Talmola                                                                                                  | Timo Toivola<br>Panu Ylihaavisto                                                                                           |

| NXP Semiconductors                                         | Vijendra Kuroodi                                                                                                        | Guru Prasad                                                                                                                      |                                                                                                                            |

| Renesas Electronics Corp.<br>(USB 3.0 Promoter<br>company) | Nobuo Furuya                                                                                                            | Philip Leung                                                                                                                     | Kiichi Muto                                                                                                                |

| Rohm Co., Ltd.                                      | Mark Aaldering<br>Kris Bahar<br>Yusuke Kondo                                                      | Arun Kumar<br>Chris Lin                                                                              | Takashi Sato<br>Hiroshi Yoshimura                                                 |

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| Samsung Electronics Co., Ltd.                       | Soondo Kim<br>Woonki Kim                                                                          | Jagoun Koo<br>Cheolho Lee                                                                            | Jun Bum Lee                                                                       |

| Seagate                                             | Alvin Cox<br>Tony Priborsky                                                                       | Tom Skaar                                                                                            | Dan Smith                                                                         |

| STMicroelectronics<br>(USB 3.0 Promoter<br>company) | Nathalie Ballot<br>Nicolas Florenchie<br>Joel Huloux                                              | Christophe Lorin<br>Patrizia Milazzo                                                                 | Federico Musarra<br>Pascal Legrand                                                |

| Tektronics, Inc.                                    | Randy White                                                                                       |                                                                                                      |                                                                                   |

| Texas Instruments<br>(USB 3.0 Promoter<br>company)  | Jawaid Ahmad<br>Richard Hubbard<br>Scott Jackson<br>Yoon Lee<br>Grant Ley                         | Win Maung<br>Lauren Moore<br>Martin Patoka<br>Brian Quach<br>Wes Ray                                 | Anwar Sadat<br>Sue Vining<br>Deric Waters                                         |

| Tyco Electronics Corp.<br>(TE Connectivity Ltd.)    | Max Chao<br>Robert E. Cid<br>Kengo Ijiro<br>Eiji Ikematsu<br>Joan Leu<br>Clark Li<br>Mike Lockyer | Jim McGrath Takeshi Nakashima Luis A. Navarro Masako Saito Yoshiaki Sakuma Gavin Shih Hiroshi Shirai | Scott Shuey<br>Hidenori Taguchi<br>Bernard Vetten<br>Ryan Yu<br>Sjoerd Zwartkruis |

| VIA Technologies Inc.                               | Terrance Shih                                                                                     | Jay Tseng                                                                                            | Fong-Jim Wang                                                                     |

#### **Pre-Release Draft Industry Reviewing Companies That Provided Feedback**

#### **Revision History**

| Revision | Date            | Description                                                                                                   |

|----------|-----------------|---------------------------------------------------------------------------------------------------------------|

| 1.0      | August 11, 2014 | Initial Release                                                                                               |

| 1.1      | April 3, 2015   | Reprint release including incorporation of all approved ECNs as of the revision date plus editorial clean-up. |

| 1.2      | March 25, 2016  | Reprint release including incorporation of all approved ECNs as of the revision date plus editorial clean-up. |

#### 1 Introduction

With the continued success of the USB interface, there exists a need to adapt USB technology to serve newer computing platforms and devices as they trend toward smaller, thinner and lighter form-factors. Many of these newer platforms and devices are reaching a point where existing USB receptacles and plugs are inhibiting innovation, especially given the relatively large size and internal volume constraints of the Standard-A and Standard-B versions of USB connectors. Additionally, as platform usage models have evolved, usability and robustness requirements have advanced and the existing set of USB connectors were not originally designed for some of these newer requirements. This specification is to establish a new USB connector ecosystem that addresses the evolving needs of platforms and devices while retaining all of the functional benefits of USB that form the basis for this most popular of computing device interconnects.

#### 1.1 Purpose

This specification defines the USB Type-C™ receptacles, plug and cables.

The USB Type-C Cable and Connector Specification is guided by the following principles:

- Enable new and exciting host and device form-factors where size, industrial design and style are important parameters

- Work seamlessly with existing USB host and device silicon solutions

- Enhance ease of use for connecting USB devices with a focus on minimizing user confusion for plug and cable orientation

The USB Type-C Cable and Connector Specification defines a new receptacle, plug, cable and detection mechanisms that are compatible with existing USB interface electrical and functional specifications. This specification covers the following aspects that are needed to produce and use this new USB cable/connector solution in newer platforms and devices, and that interoperate with existing platforms and devices:

- USB Type-C receptacles, including electro-mechanical definition and performance requirements

- USB Type-C plugs and cable assemblies, including electro-mechanical definition and performance requirements

- USB Type-C to legacy cable assemblies and adapters

- USB Type-C-based device detection and interface configuration, including support for legacy connections

- USB Power Delivery optimized for the USB Type-C connector

The USB Type-C Cable and Connector Specification defines a standardized mechanism that supports Alternate Modes, such as repurposing the connector for docking-specific applications.

#### 1.2 Scope

This specification is intended as a supplement to the existing <u>USB 2.0</u>, <u>USB 3.1</u> and <u>USB Power</u> <u>Delivery</u> specifications. It addresses only the elements required to implement and support the USB Type-C receptacles, plugs and cables.

Normative information is provided to allow interoperability of components designed to this specification. Informative information, when provided, may illustrate possible design implementations.

#### 1.3 Related Documents

- USB 2.0 Universal Serial Bus Revision 2.0 Specification

This includes the entire document release package.

<a href="http://www.usb.org/developers/docs">http://www.usb.org/developers/docs</a>

- USB 3.1 Universal Serial Bus Revision 3.1 Specification

This includes the entire document release package.

<a href="http://www.usb.org/developers/docs">http://www.usb.org/developers/docs</a>

- USB PD USB Power Delivery Specification, Revision 2.0, Version 1.2, March 25, 2016

USB Power Delivery Specification, Revision 3.0, Version 1.0a, March 25, 2016

<a href="http://www.usb.org/developers/docs">http://www.usb.org/developers/docs</a>

- USB BB USB Billboard Device Class Specification, Revision 1.0, August 11, 2014 http://www.usb.org/developers/docs

- USB BC Battery Charging Specification, Revision 1.2 (including errata and ECNs through March 15, 2012), March 15, 2012

<a href="http://www.usb.org/developers/docs">http://www.usb.org/developers/docs</a>

#### 1.4 Conventions

#### 1.4.1 Precedence

If there is a conflict between text, figures, and tables, the precedence shall be tables, figures, and then text.

#### 1.4.2 Keywords

The following keywords differentiate between the levels of requirements and options.

#### 1.4.2.1 Informative

Informative is a keyword that describes information with this specification that intends to discuss and clarify requirements and features as opposed to mandating them.

#### 1.4.2.2 May

May is a keyword that indicates a choice with no implied preference.

#### 1.4.2.3 N/A

N/A is a keyword that indicates that a field or value is not applicable and has no defined value and shall not be checked or used by the recipient.

#### 1.4.2.4 Normative

Normative is a keyword that describes features that are mandated by this specification.

#### 1.4.2.5 Optional

Optional is a keyword that describes features not mandated by this specification. However, if an optional feature is implemented, the feature shall be implemented as defined by this specification (optional normative).

#### 1.4.2.6 Reserved

Reserved is a keyword indicating reserved bits, bytes, words, fields, and code values that are set-aside for future standardization. Their use and interpretation may be specified by future extensions to this specification and, unless otherwise stated, shall not be utilized or adapted by vendor implementation. A reserved bit, byte, word, or field shall be set to zero by the

sender and shall be ignored by the receiver. Reserved field values shall not be sent by the sender and, if received, shall be ignored by the receiver.

#### 1.4.2.7 Shall

Shall is a keyword indicating a mandatory (normative) requirement. Designers are mandated to implement all such requirements to ensure interoperability with other compliant Devices.

#### 1.4.2.8 Should

Should is a keyword indicating flexibility of choice with a preferred alternative. Equivalent to the phrase "it is recommended that".

#### 1.4.3 Numbering

Numbers that are immediately followed by a lowercase "b" (e.g., 01b) are binary values. Numbers that are immediately followed by an uppercase "B" are byte values. Numbers that are immediately followed by a lowercase "h" (e.g., 3Ah) are hexadecimal values. Numbers not immediately followed by either a "b", "B", or "h" are decimal values.

#### 1.5 Terms and Abbreviations

| Term                            | Description                                                                                                                                                                                                                                        |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Accessory Mode                  | A reconfiguration of the connector based on the presence of Rd/Rd or Ra/Ra on CC1/CC2, respectively.                                                                                                                                               |

| Active cable                    | An <u>Electronically Marked Cable</u> with additional electronics to condition the data path signals.                                                                                                                                              |

| Alternate Mode                  | Operation defined by a vendor or standards organization that is associated with a SVID assigned by the USB-IF. Entry and exit into and from an Alternate Mode is controlled by the <u>USB PD</u> Structured VDM Enter Mode and Exit Mode commands. |

| Audio Adapter<br>Accessory Mode | The Accessory Mode defined by the presence of Ra/Ra on CC1/CC2, respectively. See Appendix A.                                                                                                                                                      |

| BFSK                            | Binary Frequency Shift Keying used for <u>USB PD</u> communication over VBUS.                                                                                                                                                                      |

| ВМС                             | Biphase Mark Coding used for <u>USB PD</u> communication over the CC wire.                                                                                                                                                                         |

| Captive cable                   | A cable that is terminated on one end with a USB Type-C plug and has a vendor-specific connect means (hardwired or custom detachable) on the opposite end.                                                                                         |

| СС                              | Configuration Channel (CC) used in the discovery, configuration and management of connections across a USB Type-C cable.                                                                                                                           |

| Debug Accessory<br>Mode (DAM)   | The Accessory Mode defined by the presence of Rd/Rd or Rp/Rp on CC1/CC2, respectively. See Appendix B.                                                                                                                                             |

| Debug and Test<br>System (DTS)  | The combined hardware and software system that provides a system developer debug visibility and control when connected to a Target System in Debug Accessory Mode.                                                                                 |

| Default VBUS                    | VBUS voltage as defined by the <u>USB 2.0</u> and <u>USB 3.1</u> specifications.<br>Note: where used, 5 V connotes the same meaning.                                                                                                               |

| Term                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DFP                            | Downstream Facing Port, specifically associated with the flow of data in a USB connection. Typically the ports on a host or the ports on a hub to which devices are connected. In its initial state, the DFP sources VBUS and VCONN, and supports data. A charge-only DFP port only sources VBUS.                                                                                                                                                                                               |

| Direct connect                 | The host's DFP is connected directly with no USB hub in between, either via a cable or without (e.g., thumb drive), to the device's UFP.                                                                                                                                                                                                                                                                                                                                                        |

| DRD<br>(Dual-Role-Data)        | The acronym used in this specification to refer to a USB port that can operate as either a DFP (Host) or UFP (Device). The role that the port initially takes is determined by the port's power role at attach. A Source port takes on the data role of a DFP and a Sink port takes on the data role of a UFP. The port's data role may be changed dynamically using <u>USB PD</u> Data Role Swap.                                                                                              |

| DRP<br>(Dual-Role-Power)       | The acronym used in this specification to refer to a USB port that can operate as either a Source or a Sink. The role that the port offers may be fixed to either a Source or Sink or may alternate between the two port states. Initially when operating as a Source, the port will also take on the data role of a DFP and when operating as a Sink, the port will also take on the data role of a UFP. The port's power role may be changed dynamically using <u>USB PD</u> Power Role Swap. |

| DR_Swap                        | <u>USB PD</u> Data Role Swap.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Electronically<br>Marked Cable | A USB Type-C cable that uses <u>USB PD</u> to provide the cable's characteristics.                                                                                                                                                                                                                                                                                                                                                                                                              |

| eMarker                        | The element in an Electronically Marked Cable that returns information about the cable in response to a <u>USB PD</u> Discover Identity command.                                                                                                                                                                                                                                                                                                                                                |

| Initiator                      | The port initiating a Vendor Defined Message. It is independent of the port's PD role (e.g., Provider, Consumer, Provider/Consumer, or Consumer/Provider). In most cases, the Initiator will be a host.                                                                                                                                                                                                                                                                                         |