TECHNICAL USER'S MANUAL FOR:

PC/104

# MSM486SE/SEV with smartModule SM486PC

Nordstrasse 11/F CH- 4542 Luterbach Tel.: ++41 (0)32 681 58 00 Fax: ++41 (0)32 681 58 01 Email: support@digitallogic.com Homepage: <u>http://www.digitallogic.com</u>

### COPYRIGHT © 1998- 2001 BY DIGITAL-LOGIC AG

No part of this document may be reproduced, transmitted, transcribed, stored in a retrieval system, in any form or by any means, electronic, mechanical, optical, manual, or otherwise, without the prior written permission of DIGITAL-LOGIC AG.

The software described herein, together with this document, are furnished under a license agreement and may be used or copied only in accordance with the terms of that agreement.

#### ATTENTION:

All information in this manual and the product are subject to change without prior notice.

### **REVISION HISTORY:**

| ProdSerialnumber: | Product      | BIOS    | Doc.    | Date/Vis:   | Modification:                                                                                                 |

|-------------------|--------------|---------|---------|-------------|---------------------------------------------------------------------------------------------------------------|

| From: To:         | Version      | Version | Version |             | Remarks, News, Attention:                                                                                     |

| 860xxxxxxx        | V1.0         | V2.21   | V0.90   | 02.98 FK    | New Board Version, New Man-<br>ual                                                                            |

|                   |              |         | V0.91   | 03.99 TS    | Related APP-NOTES                                                                                             |

|                   |              |         | V0.92   | 04.99 JM    | Designs added                                                                                                 |

|                   | V1.1         | V2.21   | V1.00   | 04.99 FK    | Detail modified and added                                                                                     |

|                   | V1.1A        | V2.21   | V1.10   | 07.99 FK    | J17 modified to 44pin high RM2.0                                                                              |

|                   |              |         | V1.11   | 08.99 JM    | Ethernet E2PROM values                                                                                        |

|                   |              | V2.22   | V1.12   | 09.99 JM    | Internal COM1 description im-<br>proved                                                                       |

|                   |              | V2.24   | V1.13   | 11.99 FK    | Master/Slave J40                                                                                              |

|                   |              | V2.24   | V1.14   | 12.99 FK    | Small modifications                                                                                           |

|                   | V1.1         | V2.24A  | V1.15   | 01.00 STP   | Jumpers modified, new design                                                                                  |

|                   | V1.1         | V2.24A  | V1.16   | 02.00 STP   | Former design added, minor cor-<br>rections                                                                   |

|                   | V1.1<br>V1.2 | V2.24A  | V1.17   | 04.2000 STP | LAN sample added, connectors, minor corrections                                                               |

|                   | V1.1<br>V1.2 | V2.24A  | V1.18   | 06.2000 STP | BIOS setup, RS485, J17, J51,<br>Jumperlist, FDD->LPT, DOS<br>NOVELL, minor correction                         |

|                   | V1.1<br>V1.2 | V2.24A  | V1.19   | 10.2000 STP | J51 new pin order, J3, J9 moved,<br>new design, SE= ISA/16bit, new<br>address and logo, thermopicture,<br>etc |

|                   | V1.1<br>V1.2 | V2.25   | V1.2    | 04.2001 STP | Minor corrections, watchdog.<br>thermo pictures, 16bit RAM, etc                                               |

# READ CHAPTER 2.10 TO UNDERSTAND THE ELAN400 INCOMPATIBILITIES COMPARED TO THE STANDARD PC-AT DESIGN !

# **Table of Contents**

| 1 | PREFACE                                                                                      | 7                 |

|---|----------------------------------------------------------------------------------------------|-------------------|

|   | 1.1 How to use this Manual                                                                   |                   |

|   | 1.2 Trademarks                                                                               |                   |

|   | 1.3 Disclaimer                                                                               |                   |

|   | <ul><li>1.4 Who should use this Product</li><li>1.5 Recycling Information</li></ul>          |                   |

|   | 1.6 Technical Support                                                                        |                   |

|   | 1.7 Limited Warranty                                                                         |                   |

| 2 | OVERVIEW                                                                                     | ٥                 |

| 2 | 2.1 Standard Features                                                                        |                   |

|   | 2.2 Unique Features                                                                          |                   |

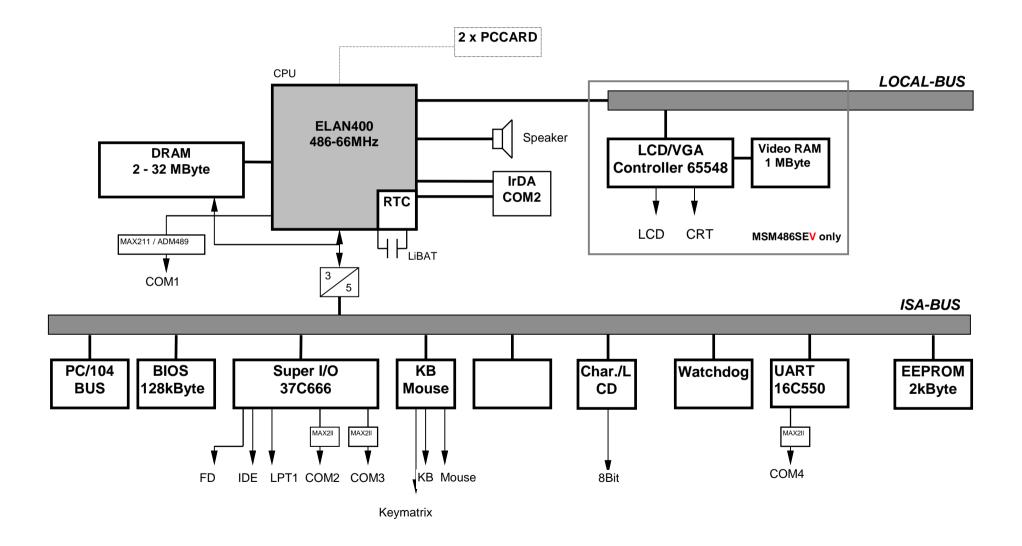

|   | 2.3 MSM486SE/V Block Diagram                                                                 | . 10              |

|   | 2.4 MSM486SE/SEV specifications                                                              |                   |

|   | 2.5 Ordering codes                                                                           |                   |

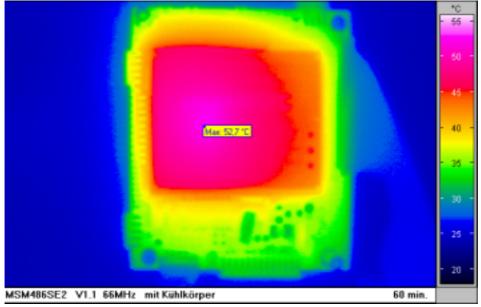

|   | <ul> <li>2.6 Thermoscan</li> <li>2.7 BIOS History</li> </ul>                                 |                   |

|   | 2.8 This product is "YEAR 2000 CAPABLE"                                                      |                   |

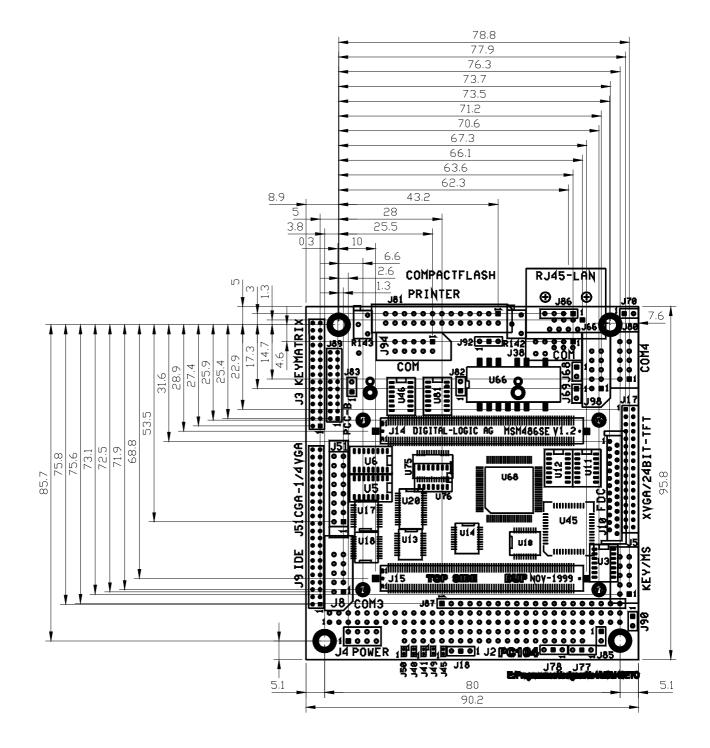

|   | 2.9 Mechanical Dimensions MSM486SE/SEV                                                       |                   |

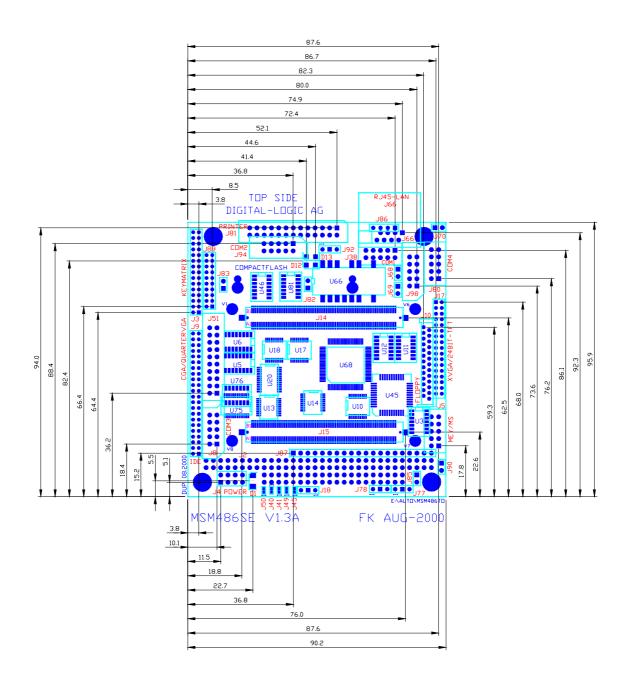

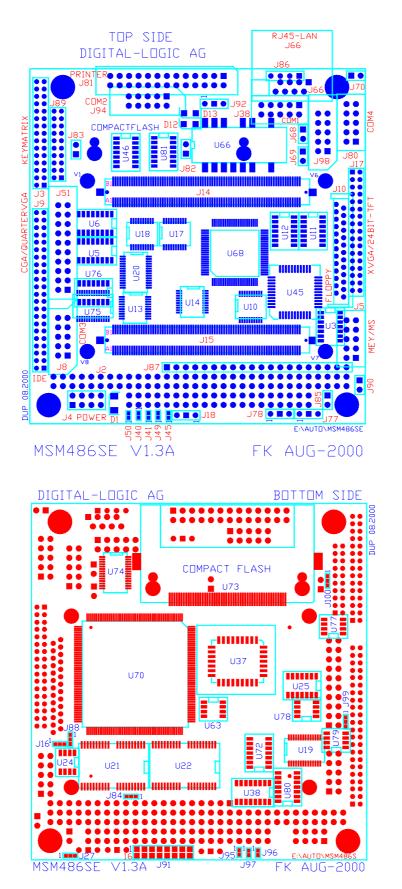

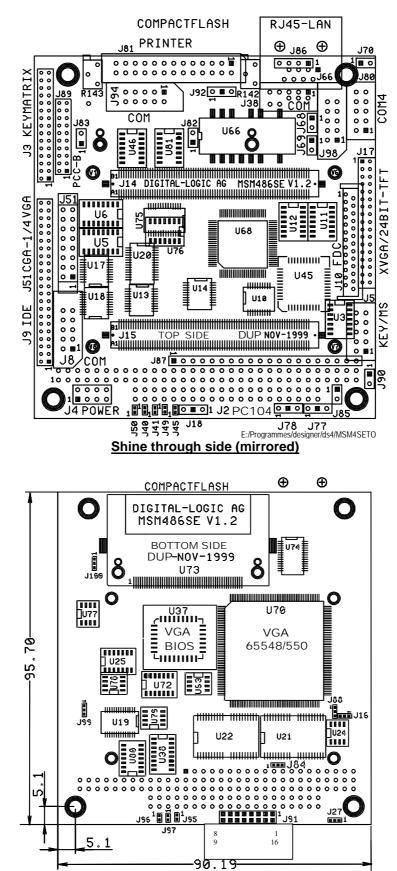

|   | 2.9.1 Boardversion V1.2                                                                      |                   |

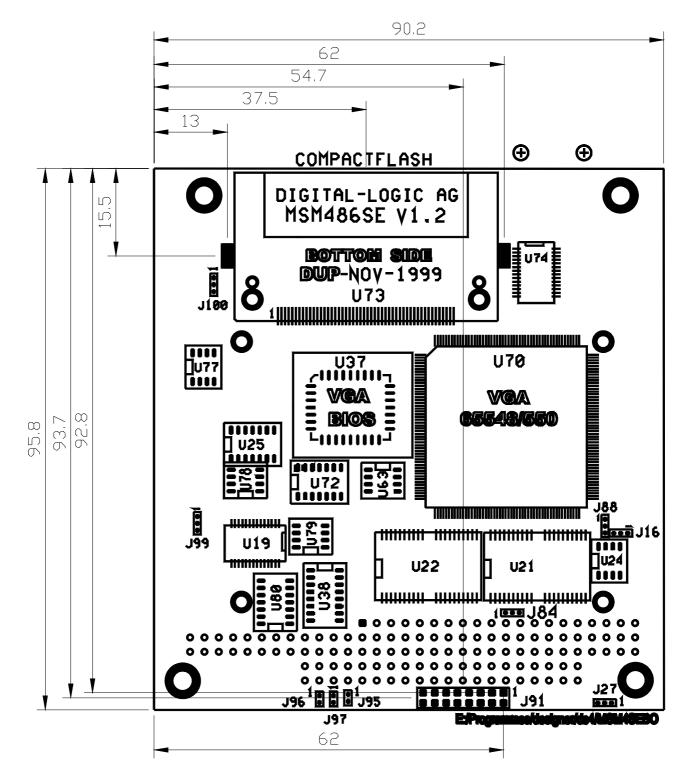

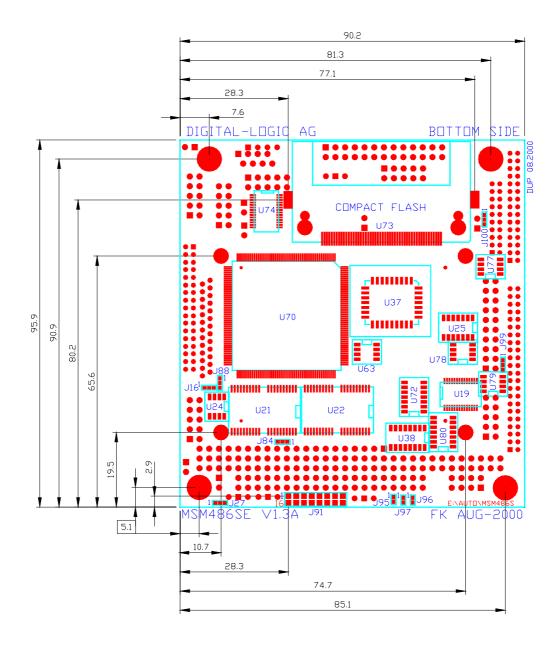

|   | 2.9.2 Boardversion V1.2                                                                      |                   |

|   | 2.9.3 Boardversion V1.3                                                                      |                   |

|   | 2.9.4 Boardversion V1.3<br>2.10 Errata for ELAN400 Rev. 4                                    | . 20<br><b>21</b> |

|   | 2.11 Related Application Notes                                                               |                   |

|   | 2.12 Incompatibilities of the ELAN400 versus the AT-PC                                       | . 22              |

|   | 2.12.1 Number of Interruptlines                                                              |                   |

|   | 2.12.2 Number of DMA-channels                                                                |                   |

|   | 2.12.3 The ELAN400 has no MASTER signal<br>2.12.4 The ELAN400 has no REFRESH signal          |                   |

|   | 2.12.5 The ELAN400 has an internal PCCARD controller, select an alternative address          |                   |

|   | 2.12.6 COM1 and COM3 port with IRQ4                                                          |                   |

|   | 2.13 Installation of the EMM386 Driver                                                       |                   |

|   | 2.14 PC/104 Bus Signals                                                                      |                   |

|   | <ul><li>2.15 Expansion Bus</li><li>2.16 High frequency radiation (to meet EN55022)</li></ul> |                   |

| _ |                                                                                              |                   |

| 3 | DETAILED SYSTEM DESCRIPTION                                                                  | -                 |

|   | 3.1 Power Requirements<br>3.1.1 Powersave Modes                                              |                   |

|   | 3.2 CPU, Board and RAMs                                                                      |                   |

|   | 3.2.1 CPU of this MICROSPACE Product                                                         |                   |

|   | 3.2.2 Numeric Coprocessor                                                                    |                   |

|   | 3.2.3 DRAM Memory                                                                            |                   |

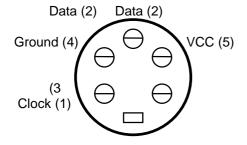

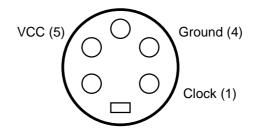

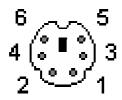

|   | 3.3 Interface<br>3.3.1 Keyboard AT-compatible and PS/2-Mouse                                 |                   |

|   | 3.3.2 Line Printer Port LPT1                                                                 |                   |

|   | 3.3.3 Serial Ports COM1-COM2-COM3                                                            | . 31              |

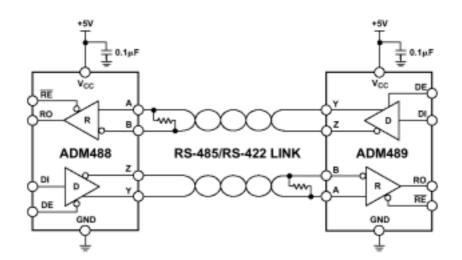

|   | 3.3.4 Serial Ports RS422 / RS485 on COM1                                                     |                   |

|   | 3.3.5 Floppy Disk Interface                                                                  |                   |

|   | 3.3.6 Speaker Interface                                                                      |                   |

|   | 3.4 Interrupts                                                                               |                   |

|   | 3.4.2 Interrupt Redirection                                                                  |                   |

|   | IRQ mapping possibilities                                                                    | . 35              |

|   | 3.5 Timers and Counters                                                                      |                   |

|   |                                                                                              |                   |

|   | 3.5.1 Programmable Timers                                                                    | . 36              |

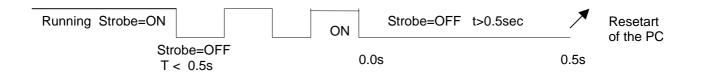

|             | 3.5.3                                                                                                                                                                                                                                   | Watchdog                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                        |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             |                                                                                                                                                                                                                                         | S                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

|             | 3.6.1                                                                                                                                                                                                                                   | ROM-BIOS Sockets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                        |

|             | 3.6.2                                                                                                                                                                                                                                   | EEPROM Memory for Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                        |

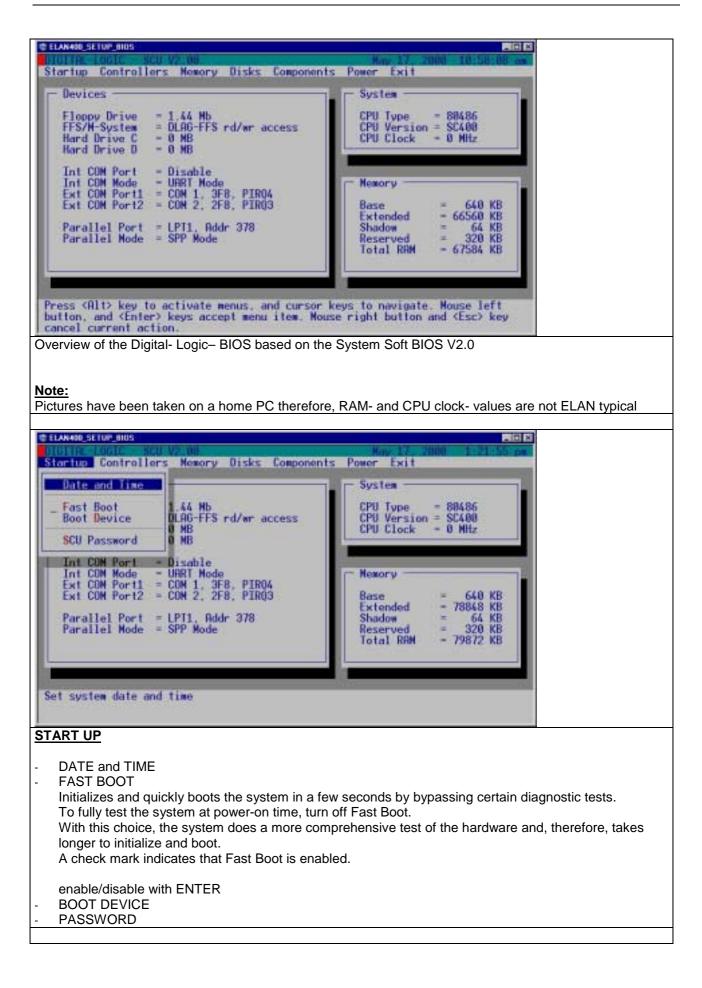

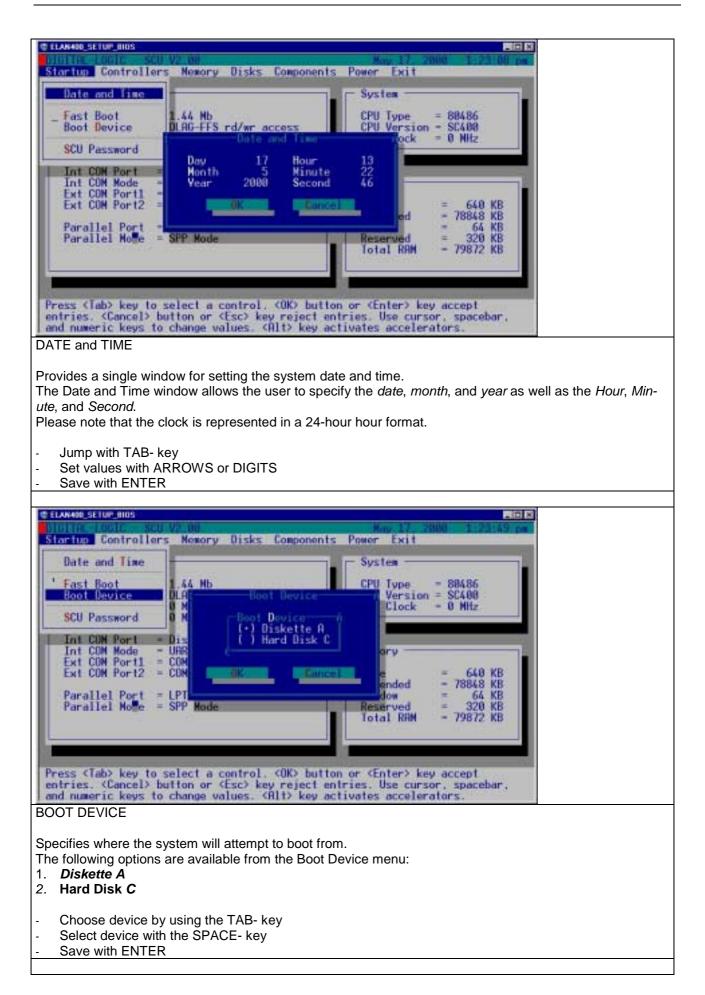

|             | 3.6.3                                                                                                                                                                                                                                   | BIOS CMOS Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                        |

|             | 3.6.4                                                                                                                                                                                                                                   | CMOS RAM Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                        |

|             | 3.6.5                                                                                                                                                                                                                                   | Harddisk PIO Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |

|             | 3.6.6                                                                                                                                                                                                                                   | EEPROM saved CMOS Setup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 45                                                                                                                                                                                                                                                                     |

|             | 3.7 Dov                                                                                                                                                                                                                                 | vnload the VGA-BIOS and the CORE-BIOS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                        |

|             | 3.7.1                                                                                                                                                                                                                                   | VGA- BIOS Download Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |

|             |                                                                                                                                                                                                                                         | nory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |

|             | 3.8.1                                                                                                                                                                                                                                   | System Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

|             | 3.8.2                                                                                                                                                                                                                                   | System I/O map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                        |

|             | 3.8.3                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                        |

|             | 3.9 VG                                                                                                                                                                                                                                  | A, LCD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 72                                                                                                                                                                                                                                                                     |

|             | 3.9.1                                                                                                                                                                                                                                   | VGA / LCD Controller 65548                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 72                                                                                                                                                                                                                                                                     |

|             | 3.9.2                                                                                                                                                                                                                                   | VGA/LCD BIOS Support                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 75                                                                                                                                                                                                                                                                     |

|             | 3.9.3                                                                                                                                                                                                                                   | Driver Resolutions and File names                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 76                                                                                                                                                                                                                                                                     |

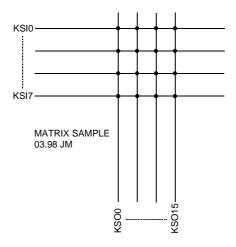

|             | 3.10 Key                                                                                                                                                                                                                                | matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 77                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                         | Define a Keymatrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |

|             |                                                                                                                                                                                                                                         | Store the Keymatrix into the EEPROM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                        |

|             | 3.10.3                                                                                                                                                                                                                                  | Read DISK-File and store to the EEPROM-Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 77                                                                                                                                                                                                                                                                     |

|             | 3.10.4                                                                                                                                                                                                                                  | Old step by step version for storing the values to another board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 78                                                                                                                                                                                                                                                                     |

|             | 3.11 The                                                                                                                                                                                                                                | ELAN400 videocontroller for ¼VGA Panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 79                                                                                                                                                                                                                                                                     |

|             | 3.11.1                                                                                                                                                                                                                                  | ELAN400-Video Panel-Definitionfile                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 80                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                         | chDOG programming                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                        |

|             |                                                                                                                                                                                                                                         | Watchdog variant B:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                        |

|             | 3.13 Eth                                                                                                                                                                                                                                | ernet IO-address and IRQ selection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                        |

|             | 3.13.1                                                                                                                                                                                                                                  | Ethernet-drivers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 85                                                                                                                                                                                                                                                                     |

|             |                                                                                                                                                                                                                                         | allation examples for IRQ11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                        |

|             | 3 1/1 1                                                                                                                                                                                                                                 | DOS NOVELL 4.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 05                                                                                                                                                                                                                                                                     |

|             | 5.14.1                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                        |

|             |                                                                                                                                                                                                                                         | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                        |

|             | 3.14.2<br>3.14.3                                                                                                                                                                                                                        | DOS CLIENT NT<br>WIN95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 85<br>86                                                                                                                                                                                                                                                               |

|             | 3.14.2<br>3.14.3<br><b>3.15 Ins</b>                                                                                                                                                                                                     | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |

|             | 3.14.2<br>3.14.3<br><b>3.15 Ins</b>                                                                                                                                                                                                     | DOS CLIENT NT<br>WIN95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                        |

| Λ           | 3.14.2<br>3.14.3<br><b>3.15 Ins</b><br>3.15.1                                                                                                                                                                                           | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                        |

| 4           | 3.14.2<br>3.14.3<br><b>3.15 Ins</b><br>3.15.1                                                                                                                                                                                           | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                        |

| 4           | 3.14.2<br>3.14.3<br><b>3.15 Ins</b><br>3.15.1<br><b>DES</b>                                                                                                                                                                             | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 85<br>86<br>86<br>86<br>86<br>86<br>87                                                                                                                                                                                                                                 |

| 4<br>5      | 3.14.2<br>3.14.3<br><b>3.15 Inst</b><br>3.15.1<br>DESC                                                                                                                                                                                  | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                        |

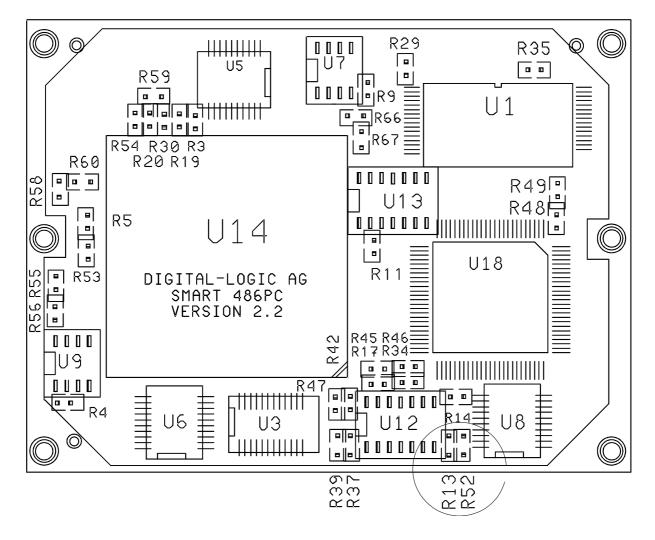

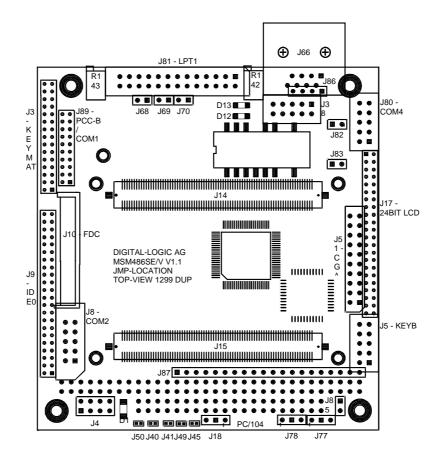

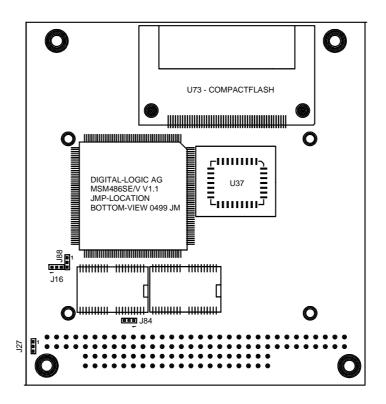

|             | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUM                                                                                                                                                                                  | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS<br>jumpers on this MICROSPACE product                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                        |

|             | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun                                                                                                                                                               | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                        |

|             | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun                                                                                                                                                               | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                        |

| 5           | 3.14.2<br>3.14.3<br><b>3.15 Ins</b><br>3.15.1<br><b>DES</b><br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3                                                                                                                                  | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>87<br>101<br>103<br>104<br>105                                                                                                                                                                                                                 |

|             | 3.14.2<br>3.14.3<br><b>3.15 Ins</b><br>3.15.1<br><b>DES</b><br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3                                                                                                                                  | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>87<br>101<br>103<br>104<br>105                                                                                                                                                                                                                 |

| 5<br>6      | 3.14.2<br>3.14.3<br><b>3.15 Ins</b><br>3.15.1<br><b>DES</b><br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED                                                                                                                           | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>101<br>103<br>104<br>105<br>106                                                                                                                                                                                                                |

| 5           | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CAB                                                                                                                               | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107                                                                                                                                                                                                  |

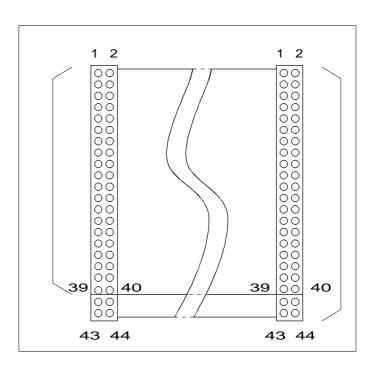

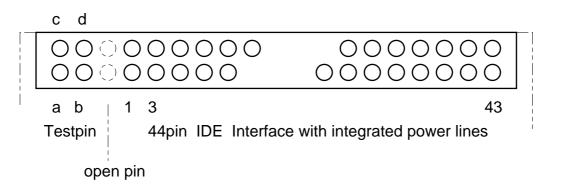

| 5<br>6      | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The                                                                                                                   | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107                                                                                                                                                                                           |

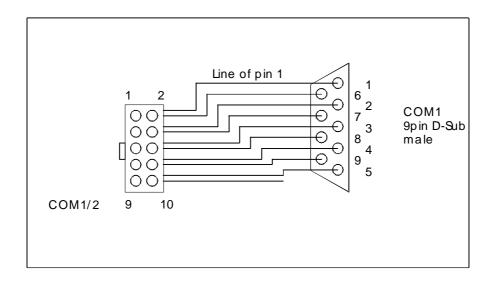

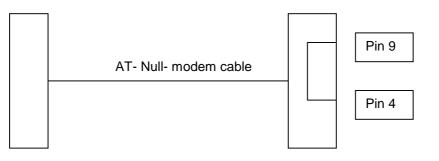

| 5<br>6      | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The                                                                                                        | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS<br>jumpers on this MICROSPACE product<br>per locations, since version 1.3 (not available yet)<br>Jumper locations, version 1.2<br>Jumper locations, until version 1.1.<br>CRITERIONS:<br>LE INTERFACE<br>harddisk cable 44 pins<br>COM 1/2 serial interface cable                                                                                                                                                                                                                      | 85<br>86<br>86<br>87<br>87<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>108                                                                                                                                                                                     |

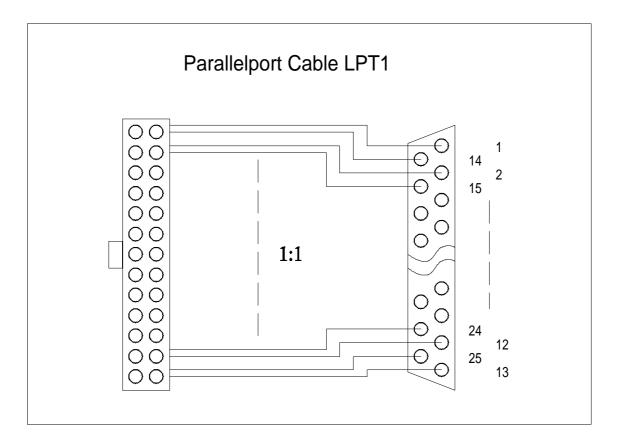

| 5<br>6      | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The                                                                                             | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS<br>jumpers on this MICROSPACE product<br>per locations, since version 1.3 (not available yet)<br>Jumper locations, version 1.2<br>Jumper locations, until version 1.1<br>CRITERIONS:<br>LE INTERFACE<br>harddisk cable 44 pins<br>COM 1/2 serial interface cable<br>Printer interface cable (J14)                                                                                                                                                                                      | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>108<br>109                                                                                                                                                                             |

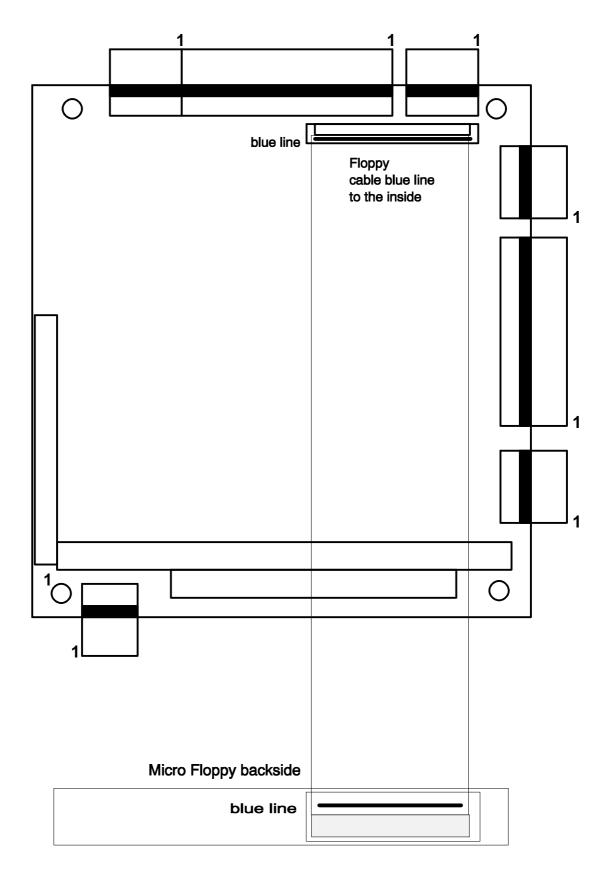

| 5<br>6      | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The                                                                                  | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>87<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>108<br>109<br>110                                                                                                                                                                       |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The                                                                                  | DOS CLIENT NT.<br>WIN95<br>allation examples for IRQ5.<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS.<br>Jumpers on this MICROSPACE product<br>per locations, since version 1.3 (not available yet).<br>Jumper locations, version 1.2<br>Jumper locations, until version 1.1.<br>CRITERIONS:<br>LE INTERFACE.<br>harddisk cable 44 pins<br>COM 1/2 serial interface cable<br>Printer interface cable (J14).<br>Micro Floppy interface cable<br>lirection FDD to LPT.                                                                                                                      | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>108<br>109<br>110<br>111                                                                                                                                                               |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec                                                                       | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>108<br>109<br>110<br>111<br>111                                                                                                                                                 |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec                                                                       | DOS CLIENT NT.<br>WIN95<br>allation examples for IRQ5.<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS.<br>Jumpers on this MICROSPACE product<br>per locations, since version 1.3 (not available yet).<br>Jumper locations, version 1.2<br>Jumper locations, until version 1.1.<br>CRITERIONS:<br>LE INTERFACE.<br>harddisk cable 44 pins<br>COM 1/2 serial interface cable<br>Printer interface cable (J14).<br>Micro Floppy interface cable<br>lirection FDD to LPT.                                                                                                                      | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>108<br>109<br>110<br>111<br>111                                                                                                                                                 |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15 Inst<br>3.15.1<br>DESC<br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CAB<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec<br>SOF<br>8.1 The<br>8.2 HD                                | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>Jumpers on this MICROSPACE product                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85<br>86<br>86<br>87<br>87<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>108<br>109<br>110<br>111<br>111<br>112<br>112                                                                                                                                    |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15 Inst<br>3.15.1<br>DESC<br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CAB<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec<br>SOF<br>8.1 The<br>8.2 HD                                | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>87<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>108<br>109<br>110<br>111<br>111<br>112<br>112                                                                                                                                    |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15 Inst<br>3.15.1<br>DESC<br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CAB<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec<br>SOF<br>8.1 The<br>8.2 HD                                | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>Jumpers on this MICROSPACE product                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85<br>86<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>108<br>109<br>110<br>110<br>111<br>111<br>112<br>112<br>112<br>113                                                                                                        |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUM<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CAB<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec<br>8.1 The<br>8.2 HD<br>8.3 Opt                                         | DOS CLIENT NT<br>WIN95<br>allation examples for IRQ5<br>DOS NOVELL 4.11<br>CRIPTION OF THE CONNECTORS<br>PER DESCRIPTIONS.<br>jumpers on this MICROSPACE product<br>per locations, since version 1.3 (not available yet).<br>Jumper locations, version 1.2<br>Jumper locations, until version 1.1.<br>CRITERIONS:<br>LE INTERFACE.<br>harddisk cable 44 pins<br>COM 1/2 serial interface cable<br>Printer interface cable (J14)<br>Micro Floppy interface cable<br>Irection FDD to LPT<br>FWARE.<br>Software Compatibility of the MICROSPACE PC<br>harddisk driver<br>erating Systems, Installation-Informations | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>107<br>108<br>109<br>110<br>111<br>111<br>112<br>112<br>112<br>113<br>113                                                                                                       |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.3 The<br>7.4 The<br>8.1 The<br>8.2 HD<br>8.3 Ope<br>8.3.1                              | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85<br>86<br>86<br>87<br>101<br>101<br>103<br>104<br>105<br>106<br>107<br>107<br>107<br>108<br>109<br>110<br>110<br>111<br>111<br>112<br>112<br>112<br>113<br>113                                                                                                       |

| 5<br>6<br>7 | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.4 The<br>7.5 Rec<br>8.1 The<br>8.3 Opt<br>8.3.1<br>8.3.2<br>8.3.3<br>8.3.4                    | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85         86         86         86         87         101         103         104         105         106         107         108         109         110         111         112         113         113         113         113         113         113         113 |

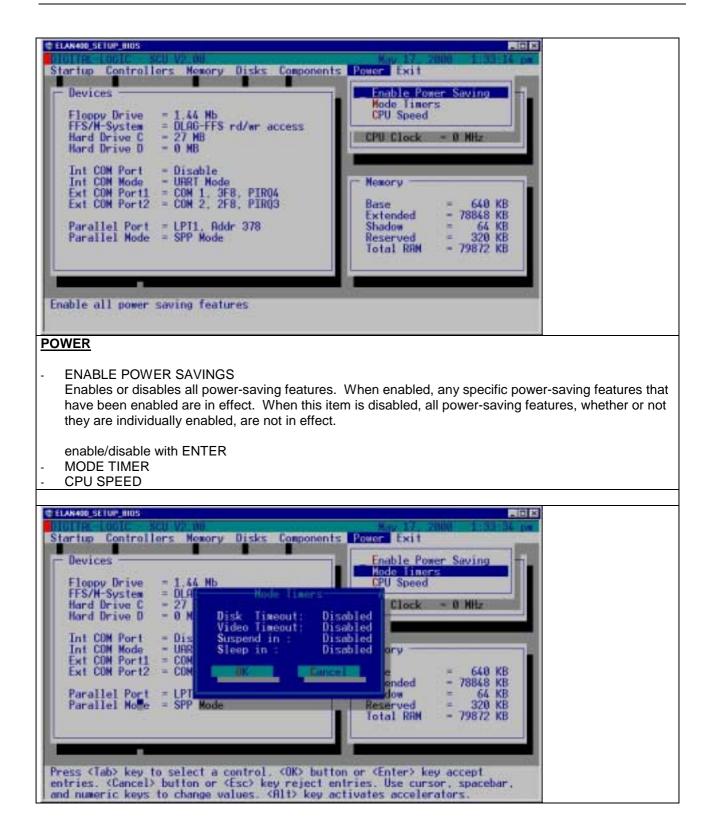

| 5<br>6      | 3.14.2<br>3.14.3<br>3.15 Inst<br>3.15.1<br>DESC<br>JUMI<br>5.1 The<br>Jun<br>5.1.2<br>5.1.3<br>LED<br>CABI<br>7.1 The<br>7.2 The<br>7.3 The<br>7.3 The<br>7.4 The<br>7.5 Rec<br>8.1 The<br>8.2 HD<br>8.3 Opt<br>8.3.1<br>8.3.2<br>8.3.3 | DOS CLIENT NT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 85         86         86         86         87         101         103         104         105         106         107         108         109         110         111         112         113         113         113         113         113         113         113 |