PLL

Eine PLL (engl.: Phase Locked Loop, Phasenregelschleife) ist ein Regelkreis, welcher einen lokalen Oszillator auf ein Eingangssignal synchronisieren kann.

Funktionsprinzip

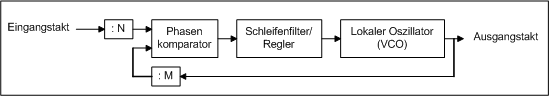

Wie jeder Regelkreis bildet er die Differenz zwischen Soll- und IST-Wert. D.h. er vergleicht die Phase eines einkommenden Signals mit der Phase des lokalen Oszillators. Dies geschieht durch einen Phasenkomparator, der je nach Anwendung und Frequenzbereich sehr verschieden aufgebaut sein kann. Die Differenz wird einem Regler zugeführt, welcher daraus ein Stellsignal für den lokalen Oszillator erzeugt. Fügt man vor dem Phasenkomparator noch optionale Frequenzteiler (Zähler) in das Eingangssignal (N) bzw. das lokale Oszillatorsignal (M) ein, kann man ein gebrochenrationales Vielfaches der Eingangsfrequenz erzeugen.

[math]\displaystyle{ f_{aus} = f_{ein} \cdot \frac{M}{N} }[/math]

Praktische Umsetzung

Eine PLL kann auf sehr viele verschiedene Arten aufgebaut sein. Voll analog, hybrid (analog-digital gemsicht) bis voll digital. Es sind sogar PLLs in Software möglich.

Anwendungen

- Demodulator für frequenzmodulierte Signale (FM-Rundfunk, UKW, Ton im analogen Fernsehen)

- Frequenzmultiplikator für Takte in CPUs, Mikrocontrollern und FPGAs.

- Taktrückgewinnung bei asynchroner Datenübertragung (Ethernet, USB, SDH, etc.)

- Trägerfrequenzsynthese für Funkgeräte und Funkempfänger (Radio, Fernsehen)

- Trägerrückgewinnung im analogen Farbfernsehen (NTSC, PAL)

- Gleichlaufsteuerung für Motoren

Hybride PLL

Hybride PLLs verwenden Digitalsignale für das Eingangs- und Ausgangssignal, arbeiten jedoch im Schleifenfilter bzw. bei der Steuerung des lokalen Oszillatos analog.

In vielen modernen Mikrocontrollern und FPGAs sind PLLs vorhanden, welche es ermöglichen, einen genauen, aber recht niederfrequenten Quarztakt mit wenigen MHz mit einem großen Faktor zu multiplizieren, um die hohen Takte von Dutzenden MHz bis mehrere GHz für heutige CPUs zu erhalten. Weiterhin kann auch die Phase des erzeugten Taktes verschoben werde. Durch eine Rückkopplung im Regelkreis wird erreicht, daß die Phasenlage stabil bleibt und dem Jitter des Eingangstaktes nur langsam folgt, wenn der Schleifenfilter der PLL entsprechend dimensioniert ist. Die Steuerung des lokalen Oszillators erfolgt voll analog mittels einer Spannung (VCO, Voltage Controlled Oscillator). Der CMOS-IC HEF4046 ist der Klassiker der hybriden PLLs.

Digitale PLL

Mittels Überabtastung mit einem sehr hohen Takt kann z.B. ein FPGA einen USB-Datenstrom ausmessen und an Hand der Pegelwechsel daraus sowohl den Takt als auch die Daten zurückgewinnen (clock and data recovery, CDR). Die Verarbeitung erfolgt voll digital, also zeitdiskret mit dem Systemtakt des FPGAs. Der Oszillator ist ein NCO (Numeric Controlled Oscillator, numerisch gesteuerter Oszillator), diese gibt es in sehr vielen verschiedenen Ausführungen. Eine populäre Variante ist die DDS. Der klassische TTL-IC 74297 enthält eine volldigitale PLL.

Software PLL

Phasenregelkreise lassen sich auch in Software nachbilden, wenn sich ein Mikrocontroller auf einen eingehenden Takt einstellt, z.B. den Nulldurchgang der Netzspannung. Mit Hilfe eines Timers kann dann ein Takt mit dem Vielfachen der Netzfrequenz erzeugt werden, welcher sychron zur Netzspannung ist. Damit kann z.B. ein digitaler Dimmer realisiert werden.