Retrocomputing auf FPGA

von Benutzer:Fpgakuechle (Volker Urban)

Dieser Artikel nimmt am Artikelwettbewerb 2012/2013 teil.

"... Er war nie auf dem College gewesen, aber, Junge, er hatte Schaltungen studiert, die von anderen stammten, und wurde allein dadurch einfach unheimlich gut. .." --Steve Wozniak

Der folgende Artikel führt an Hand eines Nachbaus eines 8-bit Computers in den Bereich des Retrocomputing mit FPGAs ein. Es wird gezeigt wie durch Nutzung von FPGA-Baugruppen, Internet-Ressourcen (Handbücher, ROM-Images, open-VHDL-Sources) und üblicher Peripherie (SVGA-Monitor, PS2-Tastatur) Jahrzehntealte Computertechnik nachgebaut werden kann. Da jeder Artikel über einen FPGA-Thema schwer zur Mutation in ein hundertseitiges Buch neigt [1] gibt dieser Artikel Praxis-Erfahrungen über ein DoItYourself Projekt an Geübte wieder und verzichtet auf die Erörterung von FPGA-Grundlagen.

In diesem Projekt wird der Z1013, ein 8-bit Computer-Bausatz von 1985 aus Ostdeutschland auf einem Xilinx Spartan-3 Starterkit nachgebaut.

Computer Bausatz Z1013

Warum Z1013?

Zum Kennenlernen der Architektur eines Computersystems ist der Z1013 wegen seiner detailierten Dokumentation ideal. Spezialchips zur Sound und Grafikausgabe gibt es nicht, man kann sich also auf den kleinsten gemeinsamen Nenner aller Computer/Controller-technik beschränken. Das Handbuch beschreibt die Interna wie Speicheraufteilung, Interruptsysten, IO-Portadressen im verständlichen Deutsch, Schaltpläne sind Bestandteil des Anhangs. Durch den geringen Speicherbedarf kann das System ohne externen Speicher auf einem LowCost-FPGA realisiert werden. Für Systeme mit einer Z80 CPU ist mit CP/M ein kommerzielles Betriebssystem und damit eine umfangreiche Nutzsoftware verfügbar. Dazu muss das Z1013 System um Massenspeicher (Emulation Diskettenlaufwerke mit 800k Speicherplatz) und Arbeitsspeicher (mindestens 64k) erweitert werden, was mit einem geeigneten FPGA-Evalboard leicht möglich ist. Homecomputer mit einer anderen CPU (6502 wie C64, Atari 800, Apple II) bieten mangels eines Betriebssystems diese Breite an Software nicht oder sind restriktiver hinsichtlich Firmware-Nutzung in Nachbauten.

Eine Z1013-FPGA System kann auch als Grundlage für den Nachbau einer ganzen Reihe von Z-80 basierenden Ost-Computer dienen. Beispielsweise des PC1715 (Quasi-Industriestandard Ostdeutschland und Russland) oder der KC-Reihe (KC-85-2/3/4) die an Hochschulen und Universitäten weit verbreitet war.

Und es gibt einen freien PC-Emulator (J1013) der bei der Entwicklung hilfreich sein kann.

Kein Nachbau nach Schaltplan

Ein Nachbau strichgenau nach Schaltplan ist nur auf dem ersten Blick leichter umsetzbar als ein Neu-Entwurf nach den ursprünglichen Vorgaben. Das Original muss mit alter, wenn nicht gar nahezu ausgestorbener Peripherie (Kassettenrekorder als Datenspeichers, Antenneneingang an einem TV-Gerät) funktionieren. Zum Entwicklungszeitpunkt waren statische RAMs größer 2k-Byte im Entwicklungsland (ehemalige DDR) nicht verfügbar und so wurden - aus strengem Preisdiktat - asynchrone dynamischen Speicher mit einem einzelnen bidirektionalen Datenport und RAS/CAS Addressmultiplex verbaut. Aber auch beim Entwurf des Apple II entschied sich Woz für DRAM. Eine DRAM-Zelle benötigt einen Transistor, SRAM dagegen um die 6. DRAM bietet so etwa 4 mal mehr Speicher für den gleichen Preis und ihm genügt ein kleineres Netzteil. [4]

Das erfordert allerdings zusätzliche Digitallogik für das Umschalten der Busse (Refreshzyklen, Bildspeicher etc.). Bei Verwendung aktueller Peripherie (SVGA-Monitor) und Bauteilen (Embedded Dual-port SRAM im FPGA) entfallen Teile der Schaltung komplett (HF-Modulator). Dual-Port RAMS benötigen keine Umschaltung zwischen CPU und Bildgenerator und können mit weniger Logikgattern aufgebaut werden.

- Schaltpläne nachgezeichnet [5]

- Schaltpläne und Belegung Lötkamm für Tastatur als Scan aus der "funkamateur" [6]

- Originalpläne (?) der ersten Bauversion Z1013.01 als grenzwertiger Scan [7]

Firmware

Die Grundsoftware für den Z1013, in PCs BIOS oder Firmware genannt, heißt hier Monitorprogramm und passt auf 2 KByte. Andere nachzuladende Software wie BASIC-Interpreter setzen auf diese Firmware auf, indem sie auf Routinen bspw. zum Auslesen der Tastatur aufsetzen, resp. diese auf vereinbarten Adressen (Sprungverteiler) aufrufen.

Peripherie

PIO

Der Hersteller der Z80 CPU entwickelte für den Anschluss weiterer Geräte wie Tastaturen oder Tapes einen Spezialschaltkreis für parallelen In- und Output (PIO). Dieser wird wie die von Mikrocontrollern bekannten GPIOs eingesetzt und generiert und bedient Interruptanforderungen an die CPU. Die PIO stellt zwei 8bit breite Ports (PORT A und PORT B) zur Verfügung, nimmt IRQ-Anforderungen andere Peripherie-IC's in der Daisy Chain entgegen und leitet sie an die CPU weiter. Die Ports müssen zu Beginn auf eine Betriebsart (Byteweise IN, Byteweise OUT, Einzelbitbetrieb,...) konfiguriert werden. Im Z1013 wird die Matrixtastatur und das Diskettenlaufwerk über die PIO gesteuert. Daher wird die Betriebsart Einzelbit benutzt und nicht wie erwartet der Intterupt-betrieb. Dadurch genügt eine teilweiser Nachbau dieses IC.

- Datenblatt der Zilog PIO [8]

Tastatur

Für den Z1013 ist eine Matrix-Tastatur vorgesehen, die von der Firmware aktiv abgefragt wird. Die Firmware wählt immer eine Spalte der Tastatur an und liest eine n bit-Zahl wobei jedes bit für eine andere Taste der Tastatur steht. Einige Modelle des Bausatzes unterstützen zwei verschiedene Matrix-Tastaturen, zusätzlich zu der Standard 8x4 Tastatur eine "Komforttastatur" mit einer 8x8 Matrix. So wurden die Tasten nicht übermäßig mehrfach belegt.

Massenspeicher

Der Z1013 lädt und speichert Anwender-programme/Daten vom Arbeitsspeicher zum einem Magnetband. Dazu werden zwei Pins der PIO benutzt. In einem FPGA-Nachbau kann man stattdessen von einem externen Speicher (Flash) direkt den RAM schreiben/speichern. Die Ansteuerung kann weiterhin über das Monitorprogramm geschehen, nur werden dabei nicht die L-oad/ S-Save Routinen benutzt. Der Flashcontroller kann als IO-Gerät an den Adressen oberhalb 0x11 eingebunden werden, die Steuerkommandos (Start/Zieladressen/Kommandos) werden mit dem Out Befehl abgesetzt. Für den Datentransfer zum Arbeitsspeicher gibt es unter anderem folgende Datenpfade:

- Dualport

- Memorycontroller

- Busarbitrierung (DMA) des Z80

Die dritte Variante eröffnet die meisten Optionen, das sie unabhängig von der Speicherarchitektur ist.

- Z80 - DMA [11]

Hochfahren und Programm Start

Programme werden nach dem Starten des Monitorprogramms mit dem L(oad) Kommando von Band geladen und mit J(ump) gestartet. Davor initialisiert sich die Hardware:

- Der Datenbus ist auf "00" gezogen, die CPU zählt den Adressbus hoch

- bei Erreichen des (P)ROMS Adressraums wird der Datenbus freigegeben und das Monitorprogramm startet

- das Monitorprogramm initialisiert die PIO zur Benutzung der Tastatur und Bandgerät

- der Anwender lädt vom Band das Programm (hier TinyBASIC) mit dem Kommando L-Kommando (L startadresse Endadresse) ,hier: "L 100 B0FF"

- das Programm wird mit einem Sprung zur Start Adresse gestartet, hier "J 100"

Auswahl FPGA-Board

FPGA-Boards gibt es zwischen rund 100 € und mehreren Tausend €uro. Fast jedes eignet sich zum Nachbau eines 8-bit Homecomputers. Die folgende Beschreibung der Hauptkomponenten soll helfen ein Board hinsichtlich seiner Eignung für Retrocomputing einzuschätzen. Das Board sollte alle nötige Hardware mitbringen.

VGA-Port

An diesem wird der Monitor angeschlossen, es gibt nur eine Bauform. Das Nachrüsten eines VGA Ports an Erweiterungsport ist möglich. Mit einem FPGA-Pin pro Grundfarbsignal wie im Spartan3-SK sind 8 Farben möglich Weiss auf Schwarz, Grün auf Schwarz, und Gelb auf Blau sind gut lesbare Kombination für Vorder- und Hintergrundfarbe. Bei eingen Evalboards sind 8 pins über Spannungsteiler mit den RGB-Leitungen, das gestattet 256 Farben. Für den Z1013 mit seiner Zeichensatzgrafik ist der VGA-Anschluss mit 3 bit Farbtiefe völlig ausreichend.

Tastaturanschluß

Ein reinrassiger USB-Anschluß ist komplexer als ein 8 Bit Computer selbst, daher sollte eine PS/2 Tastatur benutzt werden. Einige Tastaturen mit USB-Anschluß arbeiten mit einem PS/2 Adapter im sogenannten COMBO. Beim Xilinx Spartan3AN Starterkit liegen die Anschluße allerdings so beengt, das die benachtbarten RS232 Anschlüsse seitlich weggedrückt werden. Das Evalboard sollte also mit einem PS2-Anschluß ausgerüstet sein. Natürlich lässt sich eine PS2 Tastatur auch an zwei Pins und 3.3V fädeln (obwohl PS2 für 5V spezifiziert ist).

Speicher

Im Original ist der Arbeitsspeicher aus dynamischen asynchronen single Port RAM aufgebaut, der Bildspeicher aus asynchronen statischen RAM mit bidirektionalem Datenport. Der Adressbus des Bildspeichers wird über einen Multiplexer zwischen CPU und Adresszähler geteilt.

Im FPGA dagegen stehen uns mit dem BRAM synchroner statischer dual port Ram zur Verfügung, der bereits nach PowerUp initialisiert ist. Dies vereinfacht insbesonders die Beschaltung des Bildspeichers. Im Original wird der einzige Port zwischen CPU und Displaylogik mittels der Bustreiber im Adress- und Datenbus umgeschaltet. Im FPGA dagegen wird die CPU an einem Port, der nur zum Beschreiben genutzt wird angeschlossen, die Videologik an den zweiten Read-Only Port.

Zuweilen genügen die Speicherblöcke im FPGA, die 12 BRAMS Spartan3-200 sind genug für 16kB Arbeitsspeicher, 4kB ROM mit Urlader, 2kByte Zeichensatz und 1kByte Bildspeicher. Dem Betriebssystem CP/M mit typischerweise 80x24 Zeichen genügt das völlig. Dagegen benötigt Pixelgrafik schnell ein Mehrfaches, schon bei heute als grobpixelig geltenden 256 Farben.

Während Arbeitsspeicher einfach mit FPGA-externen Standard-RAM ersetzbar ist, vereinfacht interner Bildspeicher als Dual-port RAM das Systemdesign deutlich. Allerdings reicht interner RAM insbesonders der kleineren XILINX-FPGAs kaum für mehrfarbige Pixelgrafiken. Altera - FPGAs gelten hinsichtlich RAM als besser ausgestattet. Alternativ zum Embedded RAM kann ein zweiter externer SRAM eingesetzt werden. Bilddaten könnten zeilenweise zwischengespeichert und während der Blankphasen (VBlank, HBlank, Schwarzränder geschrieben werden.

| Computer | Mode | Bildspeicher | FPGA | Embedded RAM |

|---|---|---|---|---|

| Z1013 | 32x32 Zeichen | 2+1 kByte | Sparten3A-200 | 36 kByte |

| C64 | 320x200 16 Farben | 2x16 kByte | 16 | 64 kByte |

| VGA | 320x200 256 Farben | 64 kByte | EP3C40 | 126 kByte |

| SVGA | 800x600 HiColor | 960 kByte | Actel-Igloo -600 | ~25 kByte |

Dem Digilent BASYS2 Board fehlt leider jeder Speicherchip und der on-board Spartan-3 - 100 mit 2 BRAM's (4 kByte) ist zu klein um diesen Mangel auszugleichen.

Massenspeicher

Programme für 8bit Computer sind meist kleiner als der zur Verfügung stehende RAM, also 64 kB. Ein Eval-Board für Retrocomputing sollte also mindestens 64 kByte an nichtflüchtigen Speicher mitbringen, für Diskettenorientierte Systeme (C64 ca. 180 kByte; CP/M mit 400 - 800 kByte pro Diskette) deutlich mehr. Der ROM für das FPGA-Bitfile kann bis zu 128 kByte an Nutzerdaten aufnehmen, so das Platform-Flash XCF02S auf dem Spartan3 Starterkit und kann vom PC aus mit dem FPGA Programmiertool impact) beschrieben werden. Anderer Boards haben Flash Chips on Board (bspw S-3A SK mit ???). Speicher mit seriellen Interface genügt den geringen Geschwindigkeitsanforderungen.

Der Platform-ROM hat nur eine begrenzte Anzahl von Schreibzyklen, die für den xcf02s auf dem Startekit von Xilinx mit mindestens zwanzig Tausend angegeben wird. Das ist für die gelegentliche Nutzung ewig, bei intensiver Nutzung durch eine Person 10 Schreiben pro Arbeitstag noch normal endlich (8 Jahre), aber bei Nutzung in der Schulung oder als CP/M - Arbeitsrechner mit häufigen Zwischenspeichern Zum Beispiel von Basicprogrammen/Spielständen/Texten bedenklich. Zumal ein Austausch eine BGA-Reworkstation erfordert und nur begrenzt oft möglich ist. Eine SD-Karten Lösung wie in der ct beschrieben oder in den ZTEX Modulen realisiert ist der bessere Disk-Ersatz.

- Datenblatt Platform Flash [12]

- vom Ram Nutzerdaten in den FPGA lesen [13]

- SD-Karte als Konfigurations- und Datenspeicher für FPGA-Systeme [14]

FPGA-Auswahl

Das dickste Ding im Computer ist die CPU, sie ist der eine Faktor der die Auswahl des FPGA bestimmt. Als Anhaltspunkt für die Auswahl dient die Anzahl der Transistoren.

Nach Erfahrung des Autors füllt eine Z80 CPU einen S3-100, dagegen passt ein Motorola 68000 knapp in einem S3-700. Alle 8-bit CPU passen also in die kleinen, aber nicht die kleinsten FPGAs. Bei 16/32 bit Maschinen dagegen muss man sich an mittleren bis großen Typen der low-cost Baureihen halten. Bei CISC-Prozessoren kommt erschwerend hinzu, das die tiefe Logik (Addressierungsarten) die maximale Taktfrequenz drückt. So sind im Widerspruch zu PC-CPU's die älteren 8-bit Architekturen um ein schneller taktbar als die 16/32 bit Architekturen. Dies gilt nicht für auf FPGA-optimierte CPU-Cores (picoblaze, microblaze) die etwa gleichauf liegen (60-90 MHz)

| CPU | Transistorcount | Jahr, Computer | Jahr | FPGA |

|---|---|---|---|---|

| 6502 | 3 510 | Apple II, C64 | 1975 | |

| Z80 | 8 500 | CP/M-PC, Sinclair Spektrum | 1976 | Spartan3-200 (70%) |

| picoblaze | 96 slices | 8bit FPGA opt. Softcore | ? | Spartan3-50 (13%) |

| 8086 | 29 000 | XT | 1978 | |

| 68000 | 68 000 | Amiga, Apple Mac, Sun-I | 1979 | Cyclone III-25, Spartan3A-1400A |

| 286 | 134 000 | AT / MS-DOS | 1982 | |

| 68020 | 190 000 | Mac II/Sun 3 | 1984 | |

| 386 | 275 000 | full 32 bit, Linuxfähig | 1985 | |

| microblaze | 1000 slices | 32bit FPGA opt. Softcore | ? | Spartan3-200 (50%) |

Interessant ist die Lösung der Sun-1 die neben dem Motorola 68000 eine Eigenbau-MMU mitbringt und so UNIX-tauglich wird. Auffallend ist der große Unterschied zwischen einem FPGA-optimierten Softcore und einem Nachbau einer PC-CPU. Die Grenze an der eine FPGA-Implementierung noch im Hobbybereich akzeptabel ist, liegt beim Motorola 68000. Bei CPU's mit höheren Transistorcount genügen die LowCost-FPGA meist nicht und es müssen FPGA's teurer als 100€ verwendet werden.

Zusammenfassung Boardauswahl

Für den Nachbau eines 8 Systems genügen fast alle FPGA-Boards, mit Einschränkungen auch die vor 10 Jahren gefertigten. Nachrüstungen sind über die Expansionports meist einfach möglich, aber oft nicht nötig.

Für den lötfreien Einstieg:

- VGA-Port: hat mindestens 3 bit Farbcodierung (Rot, Grün, Blau) für 8 Farben, besser sind 8 bit

- PS2 Schnittstelle (3V3 sollten OK sein, obwohl PS/2 für 5V spezifiziert)

- 512kbit Flash/PROM

- RAM: 24 kB intern für die allerkleinsten 8-Biter, besser 64-128kB SRAM

- kleiner LowCost-FPGA (mindestens 200k Spartan-3)

- RS232 für eine Terminalverbindung zum PC

- 4 LED's, 3 Taster, 4x7 Segment zum schöner debuggen

Für 16 bit Computer (Commodore Amiga (MC68000))

- 1-4 MB RAM

- 4-64 MB Flash

- mittel bis großer LowCost FPGA:

- Xilinx Spartan3A XC3S1400A

- Altera Cyclone-III EP3C25E144C8

- Xilinx Spartan-6 XC6SL25

Nicetohave

- zwei RAM-Busse

- SRAM statt SDRAM

- 25+ Pins für Erweiterungen bspw D-SUB über Levelshifter/RS232 Treiber

Boardübersicht

- Bewertung einiger Xilinx und Altera Starterkits hinsichtlich Eignung für 8bit computing [17]

- Überblick über die Digilent Boards [18]

- Xilinx Starter Kits and Eval-Boards [19]

- Terasics Boards (Altera) [20]

- FPGA-Board Übersicht auf mikrocontroller.net[21]

Geräteauswahl

Monitor

Die Grafik älterer Computer mit ihrer geringen Pixelanzahl ist auch auf kleinen Flachbildschirmen gut darstellbar. Um das lästige Umstecken zwischen Entwicklungsrechner und FPGA-Board zu vermeiden wurde ein 13 Zoll Kassenmonitor (gebraucht ca. 45 €) eingesetzt.

Tastatur

PS/2 Tastaturen sind im Vergleich zu USB-Tastaturen einfach im FPGA decodierbar und daher ideal fürs Retrocomputing. Geeignete, meist ältere Tastaturen mit USB-Anschluss können über einen PS2 zu USB Adapter genutzt werden. Nicht jede Tastatur mit USB-Anschluss arbeitet mit einem PS/2-Adapter, am besten mit einem FPGA-Referenzdesign prüfen, das den Tastencode auf der Siebensegmentanzeige ausgibt. In diesem Projekt wurde eine neue flexible (Gummi-) Tastatur mit dem beigelegten USB auf PS/2 Adapter problemlos eingesetzt.

- Zum Unterschied zwischen PS/2- Tastatur, Tastatur mit USB-Anschluss und USB-Tastatur [22]

- Testdesign zum Test einer PS2-Tastatur [23]

Implementierung

Toolchain/Filestruktur

Begonnen wurde das Projekt mit einer einzigen Zielhardware - dem Xilinx Spartan3 starterkit - im Kopf. Die Dateien und der Flow sind noch für dieses Target ausgelegt, wünschenswert ist eine Trennung zwischen den Files für die unterschiedlichen Targets, wie Spartan 3-AN Evalboards, ZTEX-Spartan-6 boards, Altera DE2, Actel-FLASH FPGA's.

Die Sourcefiles wurden bereits aufgeteilt in

- Board-spezifische Dateien (Pin-definitions, wrapper, testbench) unter /Starterkit

- vom Autor für den Nachbau erstellte files /src/vhdl

- kleine Hilfsmodule (LED-blinker, 7-Seg Muxer) unter /kleinkram

- 3rd party sources aus anderen Open-Source o.ä. Projekten haben ebenfalls eigene Verzeichnisse

Dateien die sich von board zu board unterschieden wie Makefile, Pinassignments (.ucf für Xilinx) und die top-entity finden sich im Verzeichnis /board_specific. Die Dateien für das Sparta3-Starterkit liegen bspw. unter board_specific\Xilinx\Spartan-3_StarterKit.

Architekturspezifische Files wird es für das Taktsystem und den Zugriff auf den Konfig-ROM (User-Data im Platform-Flash) geben. Diese Files werden dann im Flow durch die für Altera etc ersetzt. Kleinere Unterschiede können über das generic SYSTEM ausgewählt werden und im HDL-Code ohne Dateiaustausch umgesetzt werden.

Die Steuerung über ein Makefile trägt ebenfalls zur Portierbarkeit bei. Für die Umsetzung auf Windows-pc ist das make-tool aus den GNU-tools for windows zu installieren. Mit make werden alle tools aufgerufen um aus den sourcen ein binäry für die direkte Programmierung des FPGA's zu erzeugen und ein PROM-Image für das Starterkit zu erzeugen.

- Anleitung zum Make für Xilinx [24]

- make for windows [25]

- Allgemeine makeanleitung: [26]

- Xilinx-Tools im commandline Modus [27] [28]

Synchrone BRAM ersetzen asynchrone SRAM/ROM/DRAM

Im Original sind CPU und die PIO (Parallel In/Out) mit 1 - 4 MHz getaktet, die anderen Bausteine (RAM, ROM's) arbeiten asynchron. Dagegen sind die Speicherblöcke auf dem FPGA (BRAM) synchron, müssen also mit der CPU an einem Taktnetz liegen. Um Latenzen gegenüber den originalen Taktschema zu vermeiden wird die CPU mit der entgegengesetzten (Steigend - rising) Flanke bezüglich der Speicherbausteine/PIO (Fallend - falling) betrieben.

Takt

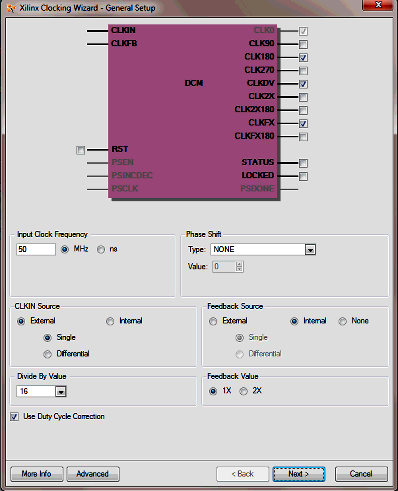

(Source: dcm_sys.vhd [1]) Für die Erzeugung des SVGA-Timing ist ein Takt von 40 MHz nötig. Auf dem Evalboard befindet sich ein Taktgenerator mit 50 MHz. Das Originalsystem wurde je nach Qualität der verbauten Schaltkreise (sogenannte Bastlertypen) mit 1, 2 oder 4 MHz betrieben. Jedes Board konnte (auf eigenes Risiko) von 1 auf 2 MHz umgelötet werden. Auch wenn das FPGA-Design deutlich schneller getaktet werden könnte, wird ein Takt nahe am Original erzeugt. Mit den vier Digitalen Clock Manager (DCM) im Spartan 3 kann der Eingangstakt geradzahlig bis 16 geteilt werden und/oder durch Digitale Frequenzsynthese (DFS) auf eine Frequenz mit einem nicht-ganzzahlige Faktor umgewandelt werden.

Für eine Umsetzung auf andere Boards muss das Taktsystem möglichst einfach sein. Deshalb wird nur eine DCM verwendet, die DFS erzeugt aus den 50 MHz den 40 MHz für das SVGA-Module und mit dem maximal möglichen Teiler von 16 wird ein Takt von 3.125 MHz für den Computer erzeugt . Der VHDL-Code (dcm_sys.vhd) wurde mit dem "architecture wizard" (Xilinx\14.3\ISE_DS\ISE\bin\nt64\arwz.exe) erstellt.

- Application Note - Using DCM in Spartan3: [29]

- Anleitung Archtecture wizard im Xilinx synthesis Guide S.23 ff. [30]

Alternativ hätte man statt mehreren Takten auch einen Takt und ClockEnable verwenden können. Dann hätte man aber auch den CPU-Core umschreiben und neu testen müssen. Da FPGA's und der Designflow mit mehreren Takten umgehen können, wäre dies kein wirklicher Gewinn an Kompatibilität oder Einfachheit. Auch werden die Taktübergänge schon in der System-Architektur abgefangen, Dual-Port Video-RAM und Handshake Signale zur Peripherie haben sich seit Anbeginn der Computertechnik bewährt.

(P)ROM-Images

ROM-Images, egal ob Monitorprogramm (ROM.vhd [2] + bm204_empty_pgk.vhd [3]) oder Zeichensatz charrom.vhd [4] + bm100_pkg.vhd [5]) liegen meist als Binärdatei vor. Für das FPGA werden diese Dateien nach VHDL konvertiert, das Image wird dabei in eine Konstante vom Typ std_logic_vector überführt.

subtype T_BM100_INDEX is integer range 0 to 2**11 - 1;

subtype T_WORD is integer range 255 downto 0;

type T_BM100_MEM is array (T_BM100_INDEX'low to T_BM100_INDEX'high) of T_word;

constant C_BM100_MEM_ARRAY_INIT : T_BM100_MEM := (

Beispiel Zeichensatz: Zuerst wird die Binärdatei zu einem lesbaren Hex-Dump umgewandelt, beispielsweise mit einem Hexeditor, dem hexlify-mode des EMACS, oder mit od (gnu-tool).

C:\Users\FPGA\ROM-Images> od -t x1 bm100.bin

0000000 ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff ff

0000160 00 00 18 24 24 18 24 42 db a5 81 ff 24 24 24 42

0000200 08 34 42 81 91 69 09 31 42 7e 81 ff 00 00 00 00

0000220 18 24 42 99 bd 99 42 24 7e 42 99 e7 00 00 00 00

Am rechten und linken Rand den Text entfernen (EMACS: "kill-rectangle"), anschließend alle Leerzeichen mit "#, 16#" ersetzen.

ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff

00#, 16#00#, 16#18#, 16#24#, 16#24#, 16#18#, 16#24#, 16#42#, 16#db#, 16#a5#, 16#81#, 16#ff#, 16#24#, 16#24#, 16#24#, 16#42

08#, 16#34#, 16#42#, 16#81#, 16#91#, 16#69#, 16#09#, 16#31#, 16#42#, 16#7e#, 16#81#, 16#ff#, 16#00#, 16#00#, 16#00#, 16#00

18#, 16#24#, 16#42#, 16#99#, 16#bd#, 16#99#, 16#42#, 16#24#, 16#7e#, 16#42#, 16#99#, 16#e7#, 16#00#, 16#00#, 16#00#, 16#00

Dann an den Rändern ergänzen, die array-Grenzen an die Filelänge anpassen und den Rest zum package ergänzen - fertig.

library ieee;

use ieee.std_logic_1164.all;

package bm100_pkg is

subtype T_BM100_INDEX is integer range 0 to 2**11 - 1;

subtype T_WORD is integer range 255 downto 0;

type T_BM100_MEM is array (T_BM100_INDEX'low to T_BM100_INDEX'high) of T_word;

constant C_BM100_MEM_ARRAY_INIT : T_BM100_MEM := (

16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#,--x00|x01

--...

16#00#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#, 16#ff#);

end package bm100_pkg;

In der zugehörigen Datei (rom.vhd resp. charrom.vhd per use Anweisungen das zu nutzende ROM-Image auswählen -> fertig.

--...

use work.bm100_pkg.all; --character ROM

--...

architecture behave of char_rom is

signal crom_array : T_BM100_MEM := C_BM100_MEM_ARRAY_INIT; --character rom

signal crom_index : T_BM100_INDEX;

--...

Natürlich funktioniert diese Vorgehensweise auch für den Arbeitsspeicher und Bildwiederholspeicher. So kann auch ohne Zuarbeit der CPU ein Bild bspw. welcome-screen angezeigt werden. Der Original-Computer kann das natürlich nicht.

Adressdekoder

(Source File: addr_decode.vhd [6])

Im Adressdecoder werden die select-Leitungen für die Speicherbaugruppen (ROM mit Monitorprogramm, Bildwiederholspeicher, Arbeispeicher) und IO-Geräte (Parallel-IO Port PIO, Tastatur-Zeilen-Ansteuerung) erzeugt. Im Original ist das mit Binär zu Dezimal-Dekodern, AND-Gattern und Diodenlogik realisiert. Im Nachbau genügen VHDL-select Anweisungen. Die Unterscheidung zwischen IO-Ports und Speicher-bereichen geschieht anhand der CPU-Signale IREQ und MREQ. Die Speicheraufteilung und IO-Adressen sind im Anhang des Z1013 Handbuchs beschrieben.

- Speicheraufteilung/IO-Adressen [31]

Ein REFRESH ist bei SRAM-Blöcken nicht nötig, daher werden die Refresh-Zyklen anhand des Refresh-Signals ausgeblendet.

Arbeitsspeicher

(Source File RAM.vhd [7]). Der Arbeitsspeicher wird als 16kx8bit array beschrieben und ist mit 8 BRAM's des FPGA realisiert. Die unscheinbare Definition von 3 Bytes an den Adressen x0000 - x0002 ersetzt die PullDowns R44-R51, das FF aus A25 und A26. Im Original wird nach dem Reset der Datenbus auf x00 gehalten, so dass die CPU NOP (No-OPeration)-Instruktionen "ausführt", also nur die Adresse auf dem Addressbus hochzählt. Erst beim Erreichen der PROM Startadresse wird der Datenbus freigegeben und das Betriebssystem wird gestartet. Im Nachbau ist an der ersten Addresse die die CPU einliest ein Sprungbefehl "gebrannt", - der Nachbau beginnt daher sofort mit der Firmware. Bei Verwendung von externen RAM ist dies nicht möglich und der datenbus muß nach dem Reset vom Speicher getrennt werden. Im Original trennt der Bustreiber A1 die CPU in zwei weiteren Fällen vom Arbeitsspeicher:

- während eine REFRESH-Zyklus und

- einer Busfreigabe für einen DMA (Direct Memory Access) über die CPU-Signale BUSRQ und BUSAK

Letztere Fall wird benötigt wenn der Speicher von einer anderen Quelle als der CPU genutzt wird. Beispielsweise beim Lesen schreiben durch einen HOST-PC über eine RS232 Schnittstelle o.ä..

Textausgabe

Der Bildspeicher (video_ram.vhd [8]) ist als Dual-Port-Speicher realisiert. Die CPU beschreibt und liest den 1 kB großen Speicher über den einen Port, der SVGA-Controller liest ihn über den zweiten Port aus. Zu Testzwecken kann die CPU vom Bildspeicher getrennt werden (Generic: G_READONLY). Der VGA-Controller stellt dann den Bildspeicher so dar wie er beim Laden das FPGA's initialisiert wurde. In dem Package video_ram_pkg.vhd [9] sind zwei Konstanten für die Initialisierung definiert. Mit C_VRAM_ARRAY_INIT stellt die wichtigsten Zeichen auf den oberen Zeilen dar:

Somit kann die Monitorausgabe überprüft werden ohne das ein Programm von der CPU abgearbeitet wird.

Dagegen füllt die andere Konstante C_VRAM_ARRAY_SPACES_INIT den Schirm mit Leerzeichen.

Der Datenausgang des Bildspeichers ist mit den oberen 8 Adressbits des Zeichengenerators (Eingang: addr_char_i) verbunden und wählt so das zu darstellende Zeichen aus. Die unteren 3 Addressbits (addr_line_i) bestimmen die aktuell auszugebende Zeile des Zeichens. Der Zeichengenerator ist als 2KByte großer ROM realisiert (Datei: charrom.vhd [10],. Ist der PROM nicht selektiert wird eine Zeile eines Leerzeichens (alle bits 0) ausgegeben.

Der Zeichensatz selbst ist im Package bm100_pkg.vhd [11] definiert. BM100 steht für "Bitmuster 100" dem Standard-Zeichensatz des Z1013. Die Originale finden sich auf [12] als Bitmuster-Dateien (siehe Erläuterungen oben). Alternativ können Zeichensätze des C64 Homecomputers benutzt werden, bspw.: [13]. Beide Computer verwenden Zeichen aus 8 mal 8 Pixeln. Auf dem SVN Server wurde ein Package mit leeren Zeichen abgelegt. Wie es mit mittels der Binärdatei modifiziert werden kann, wurde oben beschrieben.

Für die Ausgabe über die VGA-Schnittstelle nach VESA-Standard wurde der Beispielcontroller von Digilent ohne Änderungen übernommen. Auch auf mikrocontroller.net hat es ein VGA-Projekt und Hintergrund-Infos: Projekt_VGA_Core_in_VHDL. Im Modul video.vhd [14] wird der Bildspeicher ausgelesen und als RGB Signal ausgegeben. Mit 6 Schaltern auf dem Starterkit kann Vordergrund- und Hintergrundfarbe an persönliche Sehgewohnheiten angepasst werden.

- Timings mach Auflösung und Bildwiederholrate [32]

- Infos zum Z1013 Zeichensatz [33]

- Alternativer 8x8 Zeichensätze [34]

Tastatur

- kyb_emu.vhd - Umsetzer Scancode -> 8x4 Tastenmatrix [15]

- kyb_emu_pgk.vhd - Package für Konstanten (Scancode - Tasten) [16]

- kb2vhdl.vhd - (altes) PS/2 Tastatur-Interface (nicht mehr verwendet)[17]

- kb2vhdl_fk.vhd - (neues) PS/2 Tastatur-Interface [18]

Für den Anschluss der PC-Tastatur an die PIO sind zwei Module zuständig. Das erste liest über das serielle 2-Draht Interface den Code der Taste, das zweite emuliert die originale 8x4 Matrix und wie diese den Tastendruck signalisieren würde. Für das PS/2 Interface wurde zuerst ein Beispiel für das S3-Starterkit verwendet, eine nicht so gute Wahl. Das Demo setzt den Tastendruck direkt auf die 7-Segment Anzeige um und "unterschlägt" dabei die Steuercodes die anzeigen, ob die Taste gedrückt oder losgelassen wurde. Das Modul wurde daher komplett umgeschrieben, so dass der Tastencode bereits beim Drücken der Taste mit 8 bit signalisiert wird und nicht erst bei deren loslassen. Dies ist für die Erkennung einer Eingabe mit gleichzeitig gedrückter Shift-Taste unabdingbar. Tückisch ist eine Komfortfunktion der MF2-Tastatur - die automatische Tastenwiederholung (typematic). Wird eine Taste längere Zeit (typematic delay) gedrückt gehalten, wird deren scancode automatisch wiederholt (typematic rate (per second)). Daher wird die Tastatur in ein Schieberegister eingeschoben bis der Code xF0 gelesen wird. Dieser geht dem scancode voran sobald die Taste losgelassen wird. Das Zeichen wird also erst nach Loslassen der Taste angezeigt. Das neue Interface dagegen liest 8 bits nach dem Startbit und analysiert dann ob es um ein Steuerzeichen handelt (weiter Auswertung: xF0= -> Taste losgelassen, xE0 extended scancode) oder nicht (Taste gedrückt).

Der zweite Controller (Keyboardemulator) ist an den Spaltentreiber des Z1013 und an 4 auf Eingang konfigurierten Leitungen der PIO angeschlossen. Diese 4 Leitungen sind an den einen Datenausgang eines kleinen 8x4bit Speicherblocks angeschlossen. Dieser Block emuliert das originale 8x4 Speicherfeld. Eine '0' zeigt an das die entsprechende Taste gedrückt ist. Der Tastaturemulator überprüft ob ein neuer Scancode anliegt. Liegt der Scancode der (PS/2)-Shift-Taste an wird der Status entsprechend geändert und bei der Auswertung des Scancodes herangezogen. Dazu wird intern den 7 bit unteren Bits des Scancodes eine '1' vorangestellt. Aus dem Scancode wird ermittelt:

- ob eine der vier Z1013 Shifttasten zu emulieren ist

- die Spalte (1 von 8, Nummer 8 ist außen rechts) der gedruckten Taste in der originalen 4x8 Tastatur

- die One Hot Codierung der Taste auf einer der vier Zeilen ("0001" für die unterste (Shifttasten))

Die Zuordnung von Scancode zu Shift und Tastenmatrix ist in einem Record hinterlegt

CONSTANT C_ALL_KEYS : T_ALL_KEYS := (

--Index => Scancode , Shift, Col, Row

K_0 => (16#45#, S1, 1, 2), --'0'

K_0_S => (16#C5#, S1, 6, 3), --'='

K_1 => (16#16#, S1, 2, 2), --'1'

K_A => (16#1C#, NONE, 2, 1), --'A'

K_A_S => (16#9C#, S3, 2, 1), --'a'

Die Spalten (col) werden in dem Record von 1 bis 8 nummeriert, die Zeilennummer reichen von 1 bis 4. Die Shifttasten sind mit NON,S1,S2 und S3 codiert. Im FPGA wird diese codierung in einen ROM mit 7bit breiten Datenworten umgesetzt. Von deisen 7 bit stehen 2 für den SHIFTcode, 3 für die Spaltennummer und 2 für die Zeile. Die Konvertierung vom record in die 7bit Zahl realisiert die Funktion c8x4slv. Die binär codierte Zeilennummer wird in eine 1 aus 4 Codierung umgesetzt, wobei '0' für eine gedrückte Taste der 8x4 Matrix steht. Die Spaltennummer wird als Adresse, das Bitmuster der Spalte(n) als Datum für den Dualport 8x4 bit Speicher genutzt. Dieses kleine Speicherfeld "emuliert" das Tastenfeld.

Eine Stamachine setzt das Drücken bzw. Loslassen einer Taste in zwei Phasen um. Zuerst wird in der Tastermatrix die S1|S2 oder S3 Taste nachgestellt, dann die eigentliche Taste. Für sie S1-S3 Tasten wird die Spaltenadresse ausdekodiert, die Zeilennummer ist immer "1110" (unterste Zeile). Da in den vier Spalten links zwei Tasten gedrückt sein können (bspw S1 für x) wird in der zweiten Phase die zeilennummer über den zweiten Port zurückgelesen und die Zeilennummer der eigentlichen Taste hinzugefügt.

Beim Loslassen einer Taste wird für die S1|S2|S3 und für die eigentliche Taste immer "1111" geschrieben also die gesamte Spalte als "nicht gedrückt" signalisiert.

Zwischen den vier Phasen (Shift/Taste "loslassen", eigentliche Shift/Taste "drucken) die für eine Taste der PS/2 abgearbeitet werden Pausen von zirka 10 Milisekunden eingelegt, damit die Firmware auch das "Loslassen" 4x8 Tasten erkennt. Ohne diese Pausen werden von der originalen Firmware nur ein Drittel der Tasten und diese auch noch unzuverlässig erkannt.

- Ausführliche Darstellung eines VHDL-Interfaces und der Scancodes [35]

"Vor"-laden und Starten eines Programmes

Der Inhalt des Arbeitsspeicher kann bereits im VHDL-Code initialisert werden und so ein programm ohne den Umweg Ladebefehl des Monitorprogrammes geladen werden. Programme für den Z1013 liegen meist als *.z80 Dateien vor. Die ersten 32 byte enthalten als Header die Start-und die End adresse des Programmes, die folgenden bytessind ab der Startadresse in den RAM zu speichern. In den ersten 3 Bytes ist ein Sprungbefehl zum ROM abzulegen:

- Speicherabbild als Konstante anlegen:

constant C_RAM_ARRAY_INIT : T_RAM := (

16#C3#, 16#00#, 16#F0#,16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --jump to prom

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x10

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x20

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x30

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x40

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x50

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x60

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x70

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x80

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0x90

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0xA0

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0xB0

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0xC0

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0xD0

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0xE0

16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, 16#00#, --0xF0

16#c3#, 16#af#, 16#07#, 16#c3#, 16#bb#, 16#01#, 16#e7#, 16#00#, 16#c9#, 16#e7#, 16#01#, 16#c9#, 16#e7#, 16#08#, 16#c9#, 16#e7#, --0x100

--....

Der (entfernte) Header für tinyBASIC ist:

--32 byte headersave header

--0000000 00 01 ff 0b 00 01 00 00 00 00 00 00 43 d3 d3 d3

--0000020 5a 31 30 31 33 20 54 69 6e 79 2d 42 61 73 69 63

Die ersten zwei Bytes nennen die Staradresse (0100 in getauschten bytes) bytes drei und vier nennen die endadresse (ebenfalls gedreht 0bFF).

- FPGA kompilieren und laden

- Befehl "J 100" eintippen -> das Programm starten

Das Monitorprogramm muß vor dem Anwenderprogramm gestartet werden, da es die PIO konfiguriert. Ein Sprungbefehl auf die Adresse 0100 stat auf F000 in den ersten 3 Bytes des RAM's startet daher nicht korrekt.

- Beschreibung *.z80 Header [36]

- Softwarearchive Z1013 [37]

- tinyBASIC für Z1013 [38]

- Befehlsübersicht tinyBASIC [39]

Quelltexte und Compilation

Vom Autor erstellte Quellen liegen auf dem hiesigen SVN-Server (siehe Downloads). Fürs Gesamtprojekt brauchts auch Quelltexte die auf anderen Open-Source Depots lagern:

| Verzeichniss | Zweck | Woher |

|---|---|---|

| t80 | CPU (Z80) | [19] |

| VGARefComp | SVGA Controller 800x600 @ 60Hz | [20] |

Bitte die Quellen von den angegebenen Servern downladen und in die zugehörigen Verzeichnisse kopieren. Die Tastaturansteuerung wurde im Laufe des Projektes komplett neu geschrieben und liegt daher auf dem hiesigen Server.

Neben diesen VHDL-Quelltexten werden auch das ROM-Image für das Monitorprogramm benötigt. Die Originale und Hobbyisten-Varianten finden sich auf [21] als Bitmuster-Dateien (siehe Erläuterungen oben). Alternative Firmwaren gibt es dort: [22] Wie man Binärdateien nach VHDL-konvertiert wurde im Abschnitt Retrocomputing_auf_FPGA#(P)ROM-Images gezeigt.

Das Kompilieren erfolgt per make. Aufgerufen wird das make aus den GNU-Utilities for Windows [40]. Andere maketools wie nmake von microsoft sind frustrierend inkompatibel zu dem gnu-make, daher wird nur dieses unterstützt.

Sinnvolle Verwendung oder "just for fun"?

Für Steve Wozniak, den Entwickler des Apple I und II ist es keine Frage, man muss nicht studiert haben um gut in Hardware zu sein solange man Schaltungen anderer studiert und es dann selber macht.

"Wozniak: Die besten Dinge, die ich bei Apple auf die Beine gestellt habe, resultierten daraus, dass ich (a) kein Geld hatte und sie (b) noch nie zuvor gemacht hatte": ..

Livingston: Glauben Sie, dass dies das Rezept ist, um richtig gut in etwas zu sein? Wenn man es noch niemals zuvor gemacht hat und versucht, es möglichst billig hinzukriegen?

Wozniak: Yep. ... Wir hatten einen Typen, der den Macintosh entworfen hat, und der war genauso. Er war nie auf dem College gewesen, aber, Junge, er hatte Schaltungen studiert, die von anderen stammten, und wurde allein dadurch einfach unheimlich gut." [41]

Retrocomputing per Nachbau ist also eine gute Chance so gut wie der Wizard of Woz zu werden ;-) .

Debug-Module FPGA-Systeme

Viele FPGA-system nutzen Softcores (NIOS, picoblaze) zur Ansteuerung und kommunizieren mit einem Steuerrechner über RS232 (Terminalverbindung) oder Ethernet. Der Softcore parst die eingehenden Kommandos (meist in der Form RD|WR Addr data) und beschreibt/liest dann die FPGA-Register. Wie gezeigt kann auch ein komplettes (Home)-Computer system in einem FPGA generiert werden. Im Unterschied zu selbstgestrickter Softcore-Software steht eine Menge von erprobter und schlanker Software zur Verfügung z.B. BASIC. In BASIC wird mit den IN/OUT Befehlen auf Register an der Peripherie zugegriffen, mit PEEK/POKE auf Speicherbereiche. Auch kommt ein solches System ohne einen Steuerrechner aus, solange eine Tastatur und ein VGA-Display oder gar Handy-Beamer mit VGA-Eingang angeschlossen werden kann. Natürlich ist die Rechenleistung eines historischen Computersystem fern von dem eines auf FPGA's optimierten 32bit Softcores. Fürs Parametrisieren von Registern, Auslesen von Speicherbereichen und aufbereitete Ausgabe mit kurzem BASIC-Programm reicht es allemal. Und kommt ohne Megabyte an C-Compiler Umgebung und "Micro"-Linux-Cores aus.

Altrechner transportabel

Für die meisten frühen Computersysteme wurde nie eine Mobile Version entwickelt. Eine FPGA Version ist nicht nur deutlich kleiner und kann mit einer Batterie betrieben werden, da VGA-Monitore oft verfügbar sind kann der überschwere Original Monitor (meist Röhren-TV) daheim bleiben. Eine Version mit TFT Display statt Monitor wird ebenfalls möglich und bleibt wegen der Textausgabe auch bei kleinen Anzeigen lesbar.

Downloads

- Quelltexte im SVN-Sorcedepot - SVN-Zugriff: mikrocontroller.net

Foren - Diskussionen

- www.robotrontechnik.de - Thread: Z1013 auf FPGA - weiter gehts

- www.mikrocontroller.net - Thread: Artikel/Projekt Retrocomputing auf FPGA - Diskussion dazu

Web Ressourcen/Einzelnachweise

- ↑ http://www.heise.de/ct/artikel/Loetfreies-Basteln-291660.html ct-Artikel zum Lötfreien Basteln

- ↑ http://www.robotron-net.de/z1013.html Übersicht auf robotron-net.de

- ↑ http://www.jens-mueller.org/j1013/ Emulator in Java

- ↑ http://www.vectronicsappleworld.com/appleii/appleitoappleii.php Details zum Apple II Entwurf

- ↑ http://www.z1013.de/schaltplaene.html Nachgezeichnete Schaltpläne

- ↑ http://hc-ddr.hucki.net/wiki/lib/exe/fetch.php/z1013:z1013-schaltung-fa.pdf Scan aus einer DDR-Zeitschrift

- ↑ http://hc-ddr.hucki.net/wiki/lib/exe/fetch.php/z1013:z1013.01-schaltung.pdf Scan Pläne Z1013.01

- ↑ http://www.z80.info/zip/z80piomn.pdf Zilog PIO

- ↑ http://www.z1013.de/folientastatur.html Folientastatur des Z1013

- ↑ http://hc-ddr.hucki.net/wiki/doku.php/z1013:erweiterungen:tastatur Tastaturalternativen

- ↑ http://www.z80.info/zip/um0081.pdf Beschreibung des Z80 DMA S33 ff.

- ↑ http://www.xilinx.com/support/documentation/data_sheets/ds123.pdf Xilinx DS123 Platform Flash In-System PROMS

- ↑ http://www.xilinx.com/support/documentation/application_notes/xapp694.pdf Xilinx XAPP 694 Reading User data from configuration ROMs

- ↑ http://www.heise.de/ct/artikel/Loetfreies-Basteln-291660.html Artikel "Lötfreies Basteln" in der ct

- ↑ Wikipedia: Übersicht Transistoranzahl Prozessortypen

- ↑ http://forum.6502.org/viewtopic.php?f=10&t=1673 Stark schwankende Angaben für einen CPU-Nachbau

- ↑ http://members.optushome.com.au/jekent/FPGA.htm FPGA Starterkits für 8bit Retrocomputing

- ↑ http://www.digilentinc.com/Products/Catalog.cfm?NavPath=2,400&Cat=10 Digilent FPGA-Boards

- ↑ http://www.xilinx.com/products/boards-and-kits/index.htm Xilinx FPGA-Boards

- ↑ http://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=163 Terasic - Boards

- ↑ http://www.mikrocontroller.net/articles/Liste_von_FPGA_Eval_boards FPGA-Boards Übersicht auf mikrocontroller.net

- ↑ http://de.wikipedia.org/wiki/PS/2-Schnittstelle Wikipedia: PS/2 Schnittstelle

- ↑ http://www.digilentinc.com/Data/Products/S3BOARD/S3BOARD-demo.zip Gezippte PS2 Tastatur-Beispiel kb2vhdl.vhd

- ↑ http://www.xess.com/appnotes/makefile.php Makefiles for Xilinx CPLD

- ↑ http://sourceforge.net/projects/unxutils/ Sourceforge: Unixtools for Windows

- ↑ http://www.ijon.de/comp/tutorials/makefile.html Einführung in Makefiles

- ↑ http://www.xilinx.com/support/documentation/sw_manuals/xilinx13_1/devref.pdf Xilinx UG628 Xilinx Command Line tools user Guide

- ↑ http://www.demandperipherals.com/docs/CmdLineFPGA.pdf Laboranleitung Xilinx command line tools

- ↑ http://www.xilinx.com/support/documentation/application_notes/xapp462.pdf Xilinx XAPP462

- ↑ http://www.xilinx.com/itp/xilinx10/books/docs/sim/sim.pdf Xiliny Synthesis and simulation design guide

- ↑ http://hc-ddr.hucki.net/wiki/doku.php/z1013:technische_daten Speicherbereiche und IO-Adressen

- ↑ http://martin.hinner.info/vga/timing.html VGA-timings

- ↑ http://hc-ddr.hucki.net/wiki/doku.php/z1013:erweiterungen:zeichensatz Zeichensatz Z1013

- ↑ http://kofler.dot.at/c64/font_01.html Mehr Zeichensätze

- ↑ http://read.pudn.com/downloads163/doc/project/743842/FPGA%20Prototyping%20by%20VHDL%20Examples/Chapter%208.pdf Ausführliche Beispiel-Interface

- ↑ http://hc-ddr.hucki.net/wiki/doku.php/z1013:kassettenformate Beschreibung Programmformat

- ↑ http://www.z1013.de/z1013_soft.html Softwarearchive

- ↑ http://www.jens-mueller.org/j1013/z1013soft.html TinyBASIC

- ↑ http://hc-ddr.hucki.net/wiki/doku.php/z1013:software:tinybasic Übersicht tinyBASIC

- ↑ http://www.heise.de/download/gnu-utilities-for-win32-117273.html GNU Utilities für Designflow und Hexdumps

- ↑ Jessica Livingston. "Founders at Work",978-3-8266-9109-6