Nach der Verfügbarkeit des ESP32-P4 sah man im Hause Upton wohl die Notwendigkeit, die Ankündigung der zweiten Generation des hauseigenen Mikrocontrollers vorzuziehen. Neben mehr GPIOs und einem Upgrade der verwendeten ARM-Architektur gibt es die Möglichkeit, die beiden ARM-Kerne “on the fly” durch RISC/V-Cores auf Basis eines hauseigenen Designs zu ersetzen.

RISC/V und ARM im Wechsel

Der RP2040 setzte das von Espressif im ESP32 eingeführte Dual Core-Design unter Nutzung von Cortex-M0-Kernen um. Der neue Chip beschleunigt auf 150MHz und nutzt die Cortex-M33-Architektur – sie bringt eine FPU mit, und trägt so in manchen Einsatzszenarien zu einer erheblichen Performancesteigerung bei. Eine – aus Sicht des Autors interessante – Besonderheit ist, dass sich am Die neben den ARM-Kernen auch zwei als HAZARD3 (engl. für Gefahr bzw Risiko) bezeichnete RISC/V-Kerne befinden. Der Betrieb der beiden Kerne ist dabei allerdings Entweder-Oder:

1 |

RP2350 includes a pair of open-hardware Hazard3 RISC-V cores which can be substituted at boot time for the Cortex-M33 cores. Our boot ROM can even auto-detect the architecture for which a second-stage binary has been built and reboot the chip into the appropriate mode. All features of the chip, apart from a handful of security features, and the double-precision floating-point accelerator, are available in RISC-V mode. |

2 |

--- via https://www.raspberrypi.com/documentation/microcontrollers/silicon.html#architecture-switching |

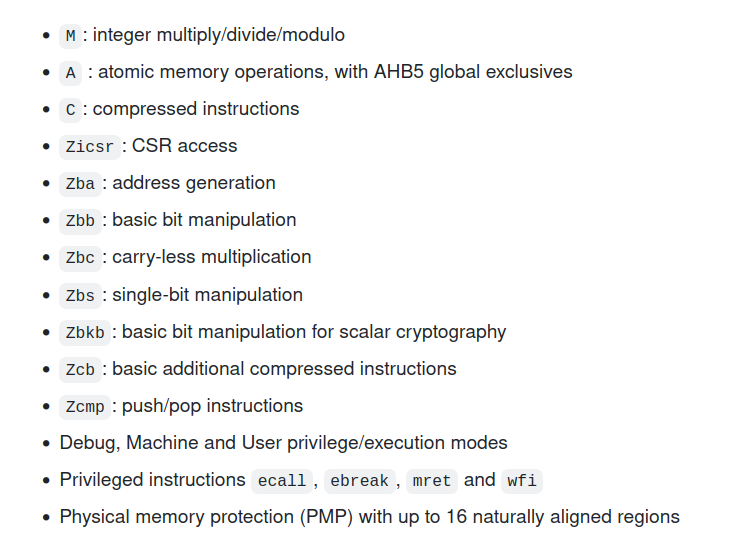

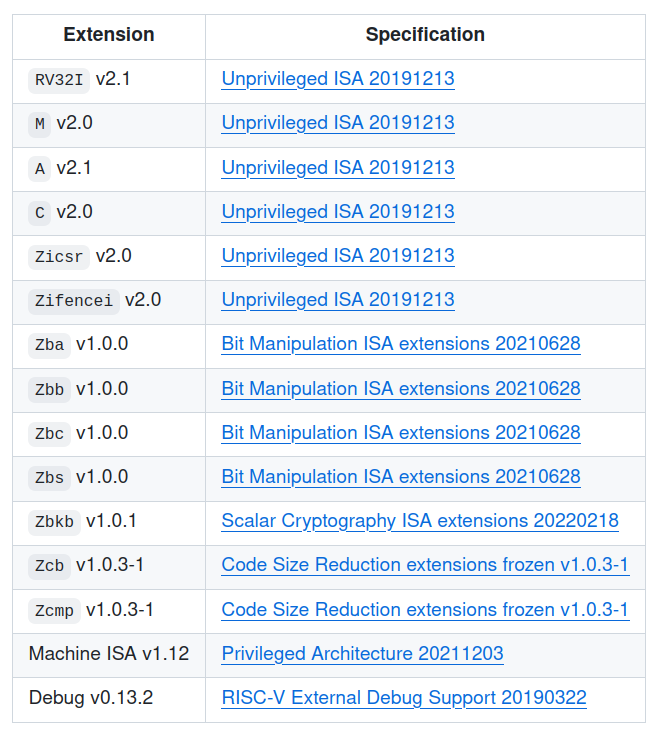

Als RISC/V-Kern kommt dabei der unter https://github.com/Wren6991/Hazard3 vom Raspberry Pi-Ingenieur Luke Wren entwickelte HAZARD3 zum Einsatz. Die Abbildungen zeigen die enthaltenen Funktionseinheiten.

Bildquelle: GitHub via https://github.com/Wren6991/Hazard3

Erweiterter Speicherausbau, RP2354 mit integriertem Flashspeicher ante portas

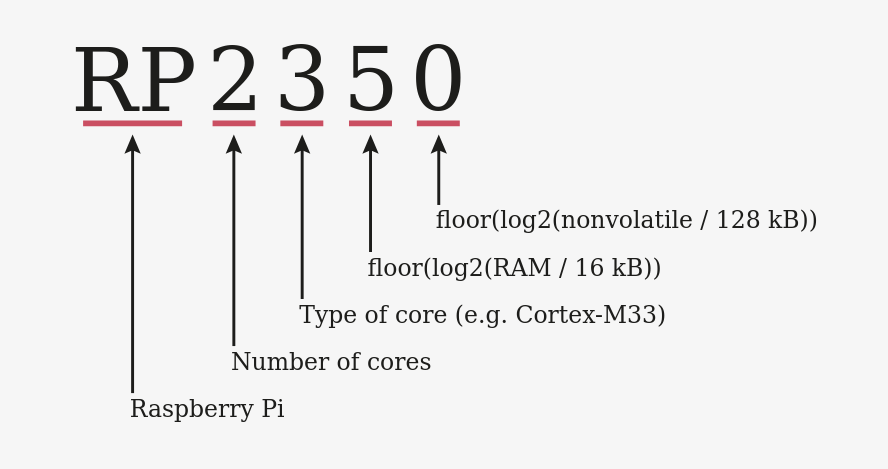

Die umfangreichen Änderungen an der Seriennummer sind unter Anderem der Erweiterung des Arbeitsspeichers geschuldet – die neue Version bringt 520 KB SRAM mit.

Bildquelle: https://www.raspberrypi.com/documentation/microcontrollers/silicon.html

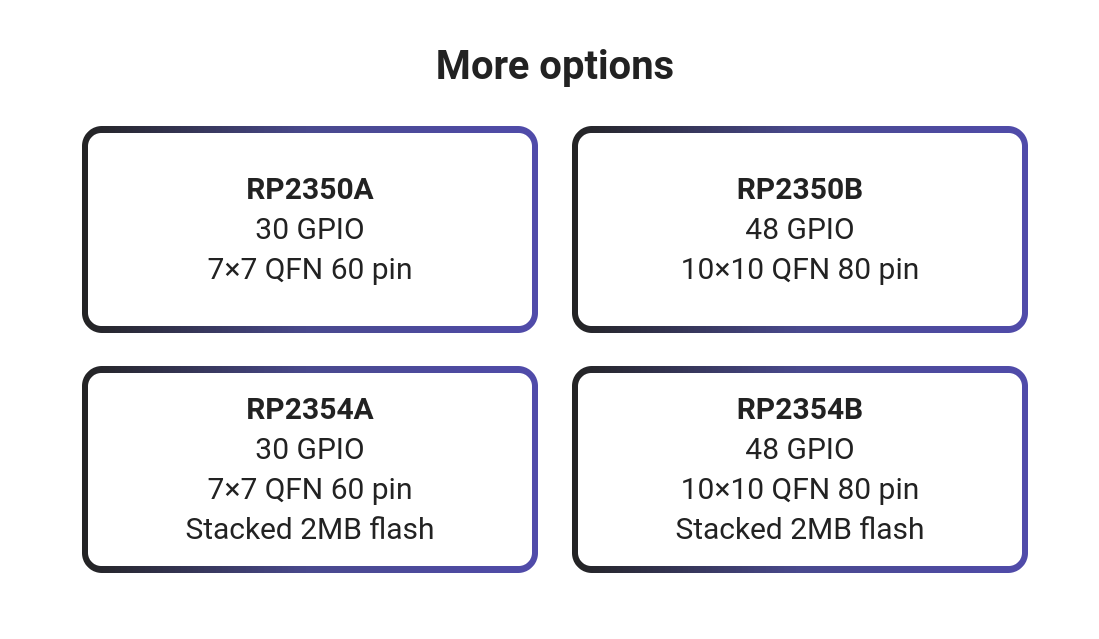

Im Rahmen der Ankündigung vermeldet die Raspberry Pi Foundation außerdem, an einer Version mit 128KB am Chip befindlichen Speicher zu arbeiten.

Bildquelle: https://www.raspberrypi.com/products/rp2350/

Mehr Peripheriegeräte dank mehr Gehäuseoptionen

Der originale RP2040 hatte ob des vergleichsweise kleinen Gehäuses nicht sonderlich viele GPIO-Pins. Der Nachfolger behebt dies wie in der obigen Abbildung gezeigt – in der Spezifikation verspricht man folgende Peripherieger#te:

1 |

Robust and fully documented security features: |

2 |

• Optional boot signing, enforced by on-chip mask ROM, with key fingerprint in OTP |

3 |

• Protected OTP storage for optional boot decryption key |

4 |

• Global bus filtering based on Arm or RISC-V security/privilege levels |

5 |

• Peripherals, GPIOs, and DMA channels individually assignable to security domains |

6 |

• Hardware mitigations for fault injection attacks |

7 |

• Hardware SHA-256 accelerator |

8 |

2 × UART |

9 |

2 × SPI controllers |

10 |

2 × I2C controllers |

11 |

24 × PWM channels |

12 |

4/8 x ADC channels |

13 |

1 × USB 1.1 controller and PHY, with host and device support |

14 |

12 × PIO state machines |

15 |

Software-compatible with RP2040 |

FreeRTOS nach wie vor im Fokus

Interessant ist auch die Frage, wie sich Raspberry Pi im Bezug auf Betriebssysteme aufstellt. Im Rahmen eines Interviews mit dem im Allgemeinen gut informierten englischen Branchennewsdienst The Register berichtet Upton folgendes:

1 |

"FreeRTOS is the preferred OS (as on RP2040). There's an increasing amount of excitement around Zephyr, and some community effort to port that to the RP2 platform, and we may engage formally with that in due course."

|

2 |

|

3 |

--- via https://www.theregister.com/2024/08/08/pi_pico_2_risc_v/ |

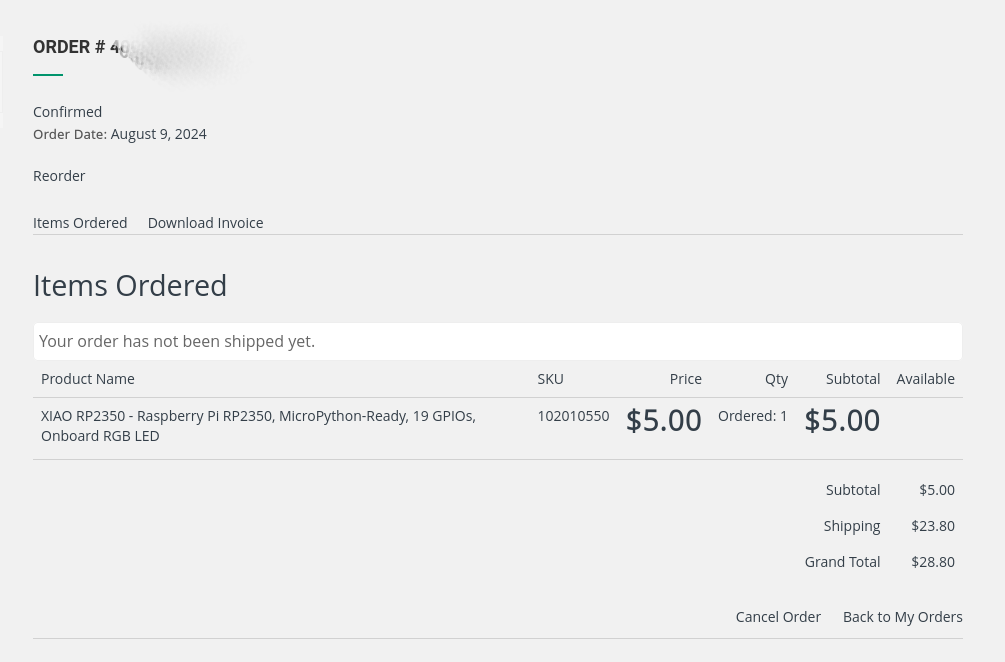

Evaluationsboards von Upton und – sofort erhältlich – bei Seeed

Im Hause Upton bietet man logischerweise ein Nachfolgemodell des Pi Pico an – der als Pi Pico 2 bezeichnete Einplatinenrechner ist derzeit allerdings nur vorbestellbar. Interessant ist, dass Seeed unter der als Bildquelle genannten URL derzeit eine alternative Platine anbietet – der Autor hat diese bereits bestellt und wird beim Eintreffen ein Update nachreichen.

Bildquelle: Autor

Dokumentation und Mehr

Wer sich in den Chip einarbeiten will, findet unter der URL https://www.raspberrypi.com/products/rp2350/ Datenblätter und sonstige Dokumentationen. Unter der URL https://datasheets.raspberrypi.com/pico/RPi-Pico-2-PUBLIC-20240708.zip? findet sich derweil die im Cadence-Format vorliegende Schaltung des Pi Pico 2.