FET

Dieser Artikel versteht sich als Unterpunkt zum Artikel Leistungselektronik

Ein FET (engl. Field Effect Transistor) ist ein Feldeffekttransistor. Der FET ist ein Bauelement, das im Gegensatz zum Bipolartransistor (engl. Bipolar Junction Transistor, BJT) mit Spannung und nicht mit Strom gesteuert wird. Weil keine P-N-Sperrschichten am Stromfluss beteiligt sind, heißen diese auch Unipolartransistoren. Unterschieden werden

- MOSFET = engl. Metall Oxide Semiconductor Field Effect Transistor; Metalloxidschicht-FET, größte Teilgruppe der FETs mit isoliertem Gate.

- JFET = engl. Junction Field Effect Transistor, Übergangszonen-FET, der steuerbare Kanal wird durch einen PN-Übergang wie in einer Diode gebildet. (Diese Diode lässt sich nachmessen und unterscheidet JFET von (selbtleitenden) MOSFET, auch wenn sie schaltungstechnisch keine Rolle spielt. Wichtig: JFETs gibt es nur selbstleitend!)

Die drei Anschlüsse eines FETs werden Gate, Drain und Source genannt. Unter Umständen ist ein vierter Anschluß vorhanden, der Bulk genannt wird. Normalerweise ist Bulk intern mit Source verbunden. Wenn dies nicht der Fall ist, muss diese Verbindung durch den Designer in der Schaltung hergestellt werden. Nicht gesichtet für Leistungstransistoren.

FET-Typen

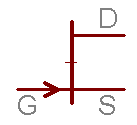

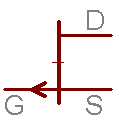

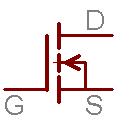

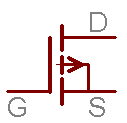

FETs werden hauptsächlich unterschieden in N-Kanal und P-Kanal, sowie "selbst sperrend = Anreicherungstyp" (engl. enhancement type) und "selbst leitend = Verarmungstyp" (engl. depletion type). Beim selbstleitenden FET ist der Transistor bei 0V Gate-Source Spannung maximal leitend (durchgesteuert) und wird durch Anlegen einer Spannung ans Gate gesperrt. Beim selbstsperrenden FET (größte Gruppe) ist der Transistor bei 0V Gate-Source Spannung gesperrt und wird durch Anlegen einer Spannung ans Gate leitend. Ist die Linie zwischen Drain und Source durchgezogen handelt es sich um einen selbstleitenden, bei einer gestrichelten Linie um einen selbstsperrenden FET. JFETs gibt es nur als Verarmungstyp.

Im weiteren Artikel wird nur der selbstsperrende MOSFET betrachtet, weil nur dieser einen althergebrachten Bipolartransistor „ersetzen“ kann.

| Typ | N-Kanal | P-Kanal |

|---|---|---|

| JFET SFET (selbst leitend) |

|

|

| MOSFET Anreicherungstyp (selbst sperrend) Enhancement Mode |

|

|

| MOSFET Verarmungstyp (selbst leitend) Depletion Mode |

|

|

Vorteile des FET

- Niedrigere Verluste als bei Bipolartransistoren.

- Sehr schnelles Schalten möglich, daher für sehr hohe Frequenzen geeignet (keine Speicherzeit wie beim BJT).

- Einfaches Parallelschalten im Schaltbetrieb, da Unterschiede im [math]\displaystyle{ R_{DS,on} }[/math] durch den positiven Temperaturkoeffizienten ausgeglichen werden.

- Leistungslose Ansteuerung im statischen Fall, jedoch hohe Umladeverluste am Gate!

- oft preiswerter als vergleichbare Bipolartransistoren (engl. Bipolar Junction Transistor, BJT)

- Relativ unempfindlich gegen Überspannung zwischen Drain und Source. Bei Überschreitung der Maximalspannung zwischen Drain und Source findet ein sogenannter "Durchbruch" statt. Dies ist vergleichbar mit dem Zener-Effekt. Ist die Energiemenge begrenzt, ist dieser Durchbruch reversibel und der FET wird NICHT zerstört. Beim Bipolartransistor ist die dafür zulässige Energiemenge viel kleiner, weil die den Strom durchquerende Fläche zu Hotspots neigt.

- Möglichkeit eines Stromfühler-Anschlusses: Durch geeignete Geometrie kann der Source-Anschluss aufgeteilt werden, etwa im Verhältnis 1:9 bis 1:99. Der Drainstrom teilt sich kontrolliert auf, auch wenn am „kleineren“ Source-Anschluss ein Messwiderstand zur Spannungs-Strom-Wandlung angeschlossen ist. Leider sind solche „Sense-MOSFETs“ selten einzeln und faktisch nie als P-Kanal-Typen verfügbar. In integrierten (Schaltnetzteil-)Schaltungen sind sie Standard.

Nachteile des FET

- Nur bedingt für hohe Spannungen geeignet, die ON-Verluste sind ab ca. 250V höher als bei einem IGBT.

- Parasitäre Diode parallel zur Drain-Source Strecke ist immer enthalten, das (Ab-)Schaltverhalten dieser Dioden ist meist schlechter als separate Dioden, was häufig zu unerwünschten Schwingungen führt.

- Empfindlicher gegen ESD am Gate als BJT

- Positiver Temperaturkoeffizient (TK), der [math]\displaystyle{ R_{DS,on} }[/math] ist stark temperaturabhängig und steigt von 25°C (Datenblattangabe) auf 150°C ungefähr um den Faktor 2. Dadurch steigen auch die Verluste und damit die Erwärmung des Bauteiles.

Erklärung der wichtigsten Datenblattwerte

| Parameter | Symbol | Beispiel | Erklärung |

|---|---|---|---|

| Drain Source Voltage (Breakdown) |

V(BR)_DSS V_DS |

75 V | Maximale Spannungsfestigkeit des Bauteiles zwischen Drain und Source |

| Continuous Drain Current | I_D(on) | 55 A @ 125 °C | Maximaler Dauerstrom bei 125°C Gehäusetemperatur |

| Pulsed Drain Current | ID_pulse I_CD(on) |

240 A | Maximaler Pulsstrom (Achtung die zulässige Zeitdauer des Pulses kann nur über die maximale Junctiontemperatur ermittelt werden) |

| Gate Charge | QGS | 320 nC | Gate-Ladung in Coloumb oder Amperesekunden, die zum Ein- oder Ausschalten des MOSFET erforderlich ist. Dies berücksichtigt die Nichtlinearität der Kapazität und (richtig?) den Miller-Effekt. Mit dieser Angabe wird der für das Schalten von Leistungs-MOSFET benötigte Gatestrom für eine bestimmte Schaltzeit ermittelt. Dieser liegt üblicherweise im einstelligen Ampere-Bereich. Moderne Typen mit extra geringer Gate-Ladung können so schneller schalten. |

| Repetetive Avalanche Energy | t_sc | 280 mJ | Maximale Energie, welche beim Avalanche Durchbruch bei Überschreiten der maximalen Drain-Source Spannung im MOSFET bei z. B. 1% Puls/Pausen Verhältnis regelmäßig auftreten darf, ohne den FET zu schädigen |

| Drain-Source ON Resistance |

RDS_ON | 0,01 Ω | Widerstand des eingeschalteten FETs bei 25°C, V_GS = 10V und ID = 30A |

| Drain-Source ON Resistance |

RDS_on | 0,021 Ω | Widerstand des eingeschalteten FETs bei 175°C, V_GS = 10V und ID = 30A |

| Thermal Resistance (junction-case) |

Rth_JC | 0,8 K/W | Thermischer Widerstand im Transistor vom der „Sperrschicht“ (junction eines Bipolartransistors, ja altmodischer Index, hier besser „Kanal“) bis zur Rückseite oder bestmöglichen Kühlmöglichkeit des Transistorgehäuses (case) |

| Gate-Source Threshold Voltage |

V_GS(th) | 2,0-4,5 V | Gatespannung, ab welcher der Transistor minimal leitend wird (I_D typisch 100-200µA), große Toleranz, typisch 1:2 zwischen Minimum und Maximum |

| Turn-on Delay | t_d(on) | 40 ns | Verzögerung zwischen dem Einschalten am Gate bis zur Reaktion im Drainstrom |

| Rise Time | t_r | 200 ns | Anstiegszeit des Transistorstromes am Drain |

| Turn-off Delay | t_d(off) | 120 ns | Verzögerung zwischen Abschalten am Gate bis zur Reaktion im Drainstrom |

| Fall Time | t_f | 60 ns | Abfallzeit des Transistorstromes am Drain |

Die oben genannten Zeiten gelten ausschließlich unter den angegebenen Messbedingungen (Gatewiderstand, Treiberspannung, sowie einer FET-Teperatur von 25°C!) und müssen für die eigene Anwendung ggf. neu berechnet werden. Meist wird man sie eher messen, weil die Rechung zu aufwändig und bisweilen unmöglich ist.

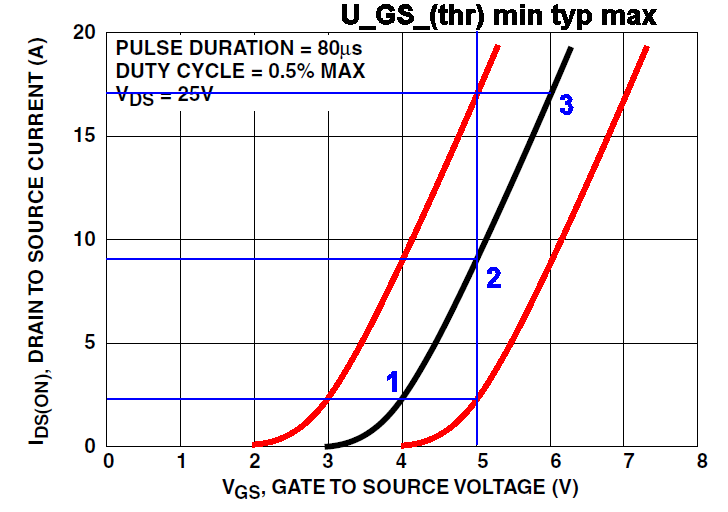

Gate-Source Threshold Voltage

Gerade bei der Gate-Source Threshold Voltage [math]\displaystyle{ V_{GS}(th) }[/math] gibt es hier immer wieder Verwirrung. Sie gibt an, ab welcher Spannung der MOSFET anfängt, minimal leitfähig zu werden. Diese Spannung ist technologisch bedingt auch heute noch einer starken Toleranz unterworfen, typischerweise hat der Bereich bei dem der FET zu leiten beginnt eine Spreizung von etwa 1:2 zwischen Minimum und Maximum. Welche Spannung man nun wirklich anlegen muss, um den gewünschten [math]\displaystyle{ R_{DS}(on) }[/math] zu erreichen kann der Tabelle im jeweiligen Datenblatt entnommen werden. Dabei unbedingt die angegebene Gatespannung beachten, nur dieser Wert ist garantiert!.

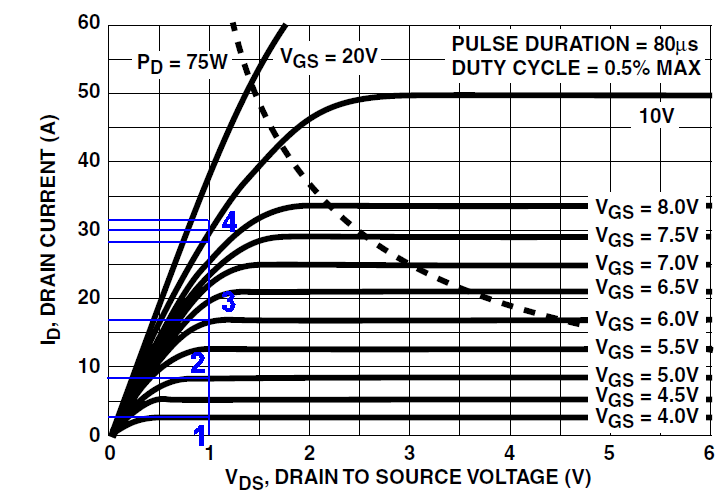

Die Kurvenschar von [math]\displaystyle{ I_D }[/math] über [math]\displaystyle{ U_{DS} }[/math] in Abhängigkeit von [math]\displaystyle{ U_{GS} }[/math] stellt immer nur typische Werte dar, keine garantierten Extremwerte (engl. worst case). Als Standardwerte kann man 10-15V für einen Standardtypen und ca. 3-5V für einen Logic Level MOSFET (LL-FET) ansetzen. Kleinsignal-FETs leiten schon ab ca 1V. Bei Ansteuerung mit 5V benötigt man also einen Typen, der sicher bei 5V voll durchgesteuert ist, z.B. IRLZ34N. Bei 3,3V ist er bereits nicht mehr zuverlässig nutzbar. Es gibt auch Typen mit noch geringerer Spannung für Vollaussteuerung. Wer einen BUZ11 ([math]\displaystyle{ V_{GS}(th) }[/math] 4V max.) mit 5V ansteuert riskiert ein Abfackeln des MOSFETs, denn je nach Toleranz kann er bereit ganz gut aufgesteuert sein oder auch nicht. Das soll in den nachfolgenden Diagrammen dargestellt werden. Zunächst die Transferkennlinie. Sie gibt an, wieviel Drainstrom in Abhängigkeit der Gatespannung fließen kann, wobei die Drainspannung konstant ist, hier im Beispiel 25V. Ein typischer BUZ11 (mittlere, schwarze Kurve) fängt bei 3V zu leiten an und erreicht bei 6V am Gate ca. 17A. Erwischt man nun ein kritisches Exemplar, das erst bei 4V zu leiten anfängt (rechte, rote Kurve um 1V parallel verschoben), so kann dieser bei 6V nur 8A leiten, für 17A braucht er 7V. Der günstige Fall, daß der BUZ11 schon bei 2V anfängt zu leiten sieht man in der linken, roten Kurve.

Wenn man die drei Fälle (min, typ, max) mit 5V ansteuert, erhält man die Arbeitspunkte 1-3 mit einem maximal schaltbaren Drainstrom von 2,5, 8 und 17A. Diese kann man in das Ausgangskennlinienfeld übertragen. Wir nehmen max. 1V U_DS an. Es ergeben sie die gleichen Ströme. Der maximale Drainstrom weicht um -5,5/+9A vom typischen Fall ab. Erhöht man nun die Gate-Source Spannung auf 10V (Arbeitspunkt 4), schwankt der maximal schaltbare Drainstrom nur noch um -2/+2A, außerdem liegt er mit 30A deutlich höher. Der BUZ11 ist somit sicher durchgesteuert.

Parasitäre Diode

Der Schwerpunkt in der FET-Entwicklung liegt auf den geringst-möglichen [math]\displaystyle{ R_{DS}(on) }[/math], die Diode entsteht auf Grund des Herstellungsprozesses, und wird nur nachrangig verbessert, da viele Optimierungsversuche auch einen Einfluss auf wichtige Kennwerte des FETs hatten und haben. Daher muss sorgfältig geprüft werden, ob die Schaltgeschwindigkeit, die Recovery-Time und die damit verbundenen Verluste sowie die dabei erzeugte unerwünschte EMV-Abstahlung tolerierbar ist, oder nicht. Hier hilft es oft eine optimierte Diode / Schottky-Diode zum FET parallel zu schalten. Ganz ausblenden läßt sich die parasitäre Diode jedoch nicht, jedoch kann man den Anteil des Stromes beeinflussen, der über die intere Diode fliest.

| Parameter | Symbol | Beispiel | Erklärung |

|---|---|---|---|

| Continuous Current | I_S | 75A | Maximaler Dauerstrom der parasitären Diode, meist identisch zum maximalen Dauerstrom des MOSFETs |

| Forward Voltage | V_SD | 1,3V | Spannungsfall an der parasitären Diode |

| Reverse Recovery Time | t_rr | 120ns | Zeit, welche die Elektronen brauchen um aus der leitenden Diode vollständig abzufließen. Während dieser Zeit fließt der Strom in Rückwärtsrichtung durch die Diode und erzeugt relativ viel Verlustleistung. |

| Reverse Recovery Charge | Q_rr | 60nC | Ladungsmenge, die während t_rr rückwärts durch die Diode fließt. |

Haupttypen und Gatespannungslevel

Unterschied N-Kanal / P-Kanal FET

Im Schaltsymbol werden die MOSFET-Typen meist durch die Pfeilrichtung in der Mitte des Symbols (eigentlich "Bulk") vom oder zum Gate unterschieden. Zeigt der Pfeil zum Gate hin, handelt es sich um einen N-Kanal-FET, zeigt der Pfeil vom Gate weg um einen P-Kanal FET.

Der große Vorteil des N-Kanal FETs (Elektronenleitung) ist, daß er immer niederohmiger ist, als ein gleich großer P-Kanal FET (Löcherleitung). Daher sind P-Kanal Typen bei vergleichbaren Werten auch immer größer = teuerer da weniger Chips auf einem Wafer Platz haben.

Beim N-Kanal FET muss die Gatespannung positiv gegenüber Source sein. Dabei wird der FET dann leitend, wenn die sogenannte "threshold voltage" (Schwellenspannung) erreicht wird. Eine typische Anwendung ist z. B. ein Low-Side Schalter: Source an GND, Drain an die Last, Ansteuerung des N-Kanal FETs mit 12V gleichbedeutend mit 12V ÜBER den Source = GND Potential.

Beim P-Kanal FET als HS-Schalter muss die Gatespannung negativer=niedriger als das Sourcepotential sein.Beispiel. Beispiel: Lastspannung = 400V d.h. Source an 400V, Last zwischen Drain und GND, Ansteuerung des P-Kanal FETs mit 388V, also 12V UNTER dem Sourcepotential.

Beim N-Kanal FET als HS-Schalter muss die Gatespannung positver=höher als das Sourcepotential sein. Beispiel: Lastspannung = 400V d.h. Drain an 400V, die Last zwischen Source und GND, Ansteuerung des N-Kanal FETs mit 412V, also 12V ÜBER dem Sourcepotential. In diesem Fall ist aber eine zusätzliche Spannungsquelle erforderlich, denn der FET wird mit einer Spannung über der Lastspannung eingeschaltet.

Weblinks

- A primer on high-side FET load switches (Part 1 of 2), Qi Deng, Senior Product Marketing Manager, Mixed-Signal Products, Micrel, Inc., 5/3/2007 4:14 PM EDT, www.eetimes.com

- A primer on high-side FET load switches (Part 2 of 2), Qi Deng, Senior Product Marketing Manager, Mixed-Signal Products. Micrel, Inc., 5/7/2007 1:36 PM EDT, www.eetimes.com

- AN804 P-Channel MOSFETs, the Best Choice for High-Side Switching (PDF) von Vishay Siliconix

Unterschied Logic-Level / „Normal“-Level

Den meisten FETs ist gemein, daß sie mit einer Spannung von 10..15 V angesteuert werden müssen, um den minimalen Einschaltwiderstand zu erreichen. Diese FETs lassen sich nicht ohne weiteres mit einem CMOS-Pegel von 5V ansteuern. Es gibt jedoch für diesen Anwendungsfall sogenannte „Logic Level“ (LL) FETs, die schon bei einer Gatespannung von etwa 4,5V voll durchgesteuert sind. Einige Kleinsignal-FETs sind schon ab ca. 1,2V voll durchgesteuert.

Hochvolt-MOSFETs für Schaltnetzteil-Anwendungen gibt es faktisch nie als Logic-Level-Typen, weswegen Ansteuerschaltkreise wie UC3842 eine Unterspannungsabschaltung bei 10 V haben. Um Steuerleistung zu sparen ist hier die (niedrige) Gate-Ladung (gate charge) der wichtigere Kennwert.

Die Schaltschwelle ergibt sich aus Dotierung und Chipgeometrie. Diese muss für Logic-Level-Typen besonders engtoleriert gehalten werden da ein „zu niedrig“ zur Selbstleitung führt (= Depletion Mode MOSFET) — ein unerwünschtes Betriebsverhalten. Das ist auch der Grund, warum die berühmt gewordene Standard-CMOS-Serie 4000 mit relativ hoher Spannung betrieben wurde, ganz zu schweigen von NMOS (12 V, dazu -5 V Substratvorspannung: EPROM 2708) oder gar PMOS (27 V): „Logic Level“, damals 5 V Logikspannung, war für MOSFET noch nicht sicher beherrschbar und hat allenfalls komplementär funktioniert.

Beispiel zur Bauteiledimensionierung

Spannungsfestigkeit

Die höchste vorkommende Betriebsspannung + Abschaltüberspannung soll kleiner als ca. 80% der Spannungsfestigkeit des Bauteiles sein.

Achtung: Zwischen dem je nach Anwendungsfall erforderlichen Pufferkondensator und dem FET wird es immer eine parasitäre Induktivität geben. Abhängig von Schaltgeschwindigkeit und Induktivität wird im Schaltmoment eine mehr oder weniger große Übrspannungsspitze produziert. Dieser Peak addiert sich auf die aktuelle Versorgungsspannung.

Überschlagsrechnung als Beispiel:

- Schaltgeschwindigkeit: dI/dt = -100A/µs (= Abschalten von 5A innerhalb 50ns),

- Induktivität: L = 1µH (~ 1 m loses, ungebündeltes Kabel)

- dU=-L*dI/dt = -1µH * (-100A / 1µs) = 100V

Dies bedeutet, daß an der "Induktivität" zwischen Transistor und Kondensator - Aufgrund von Selbstinduktion im Schaltmoment - ein Überspannungspuls von ca. 100V entsteht, der auf die Betriebsspannung aufzuschlagen ist, also lieber die Leitung kürzer machen, und - sofern möglich - nicht ganz so schnell schalten.

Stromtragfähigkeit

In jedem Datenblatt ist eine Stromtragfähigkeit bei 25°C, und meist noch bei einer höheren Temperatur z.B. 125°C, 150°C oder 175°C Kühlfahnentemperatur angegeben. Dieser Wert ist als ERSTE Entscheidungsgrundlage ausreichend, aber aus der theoretisch abführbaren Verlustleistung errechnet, und

- dient zum qualitativen Vergleich von Transistoren bezüglich ihres R_ds(on) und ihres Wärmewiderstands.

- ist für die Dimensionierung einer Schaltung nur als Richtwert zu interpretieren.

- ist ohne Schaltverluste genannt, und daher nur für einen Schaltbetrieb von wenigen Hz gültig. Außerdem wird ein annähernd idealer Kühlkörper unterstellt, der trotz der Verlustleistung das Gehäuse des Transistors auf der angegebenen Temperatur halten kann.

- entbindet einen nicht davon den Kopf einzuschalten... siehe die nachfolgenden Zeilen.

- Liegt der Strom für den die Schaltung entwickelt wird mit ca. 10..20% Abstand unter dem Datenblattwert von 125°C ist dieses Bauteil vermutlich verwendbar (siehe Detailberechnungen unten !).

- Ist der benötigte Strom im Bereich oder größer als der zulässige bei 125°C sollte entweder ein anderer Typ eingesetzt oder mehrere FETs des gleichen Typs parallelgeschaltet werden.

Verlustleistung

Hier wird eine Näherung für eine getaktete Anwendung betrachtet. In einem Transistor treten sowohl beim Ein- und Ausschalten, als auch während der Einschaltphase Verluste im Bauteil auf. Diese Verluste führen zu einer Bauteilerwärmung. Die dabei entstehende Temperatur darf die maximal zulässige Bauteiletemperatur nie überschreiten. Bei den ersten Projekten ist zu empfehlen eine berechnete Chiptemperatur von ca. 125°C nicht zu überschreiten. Fast alle aktuell verfügbaren FETs nennen im Datenblatt eine Temperatur von 175°C als ihre maximale Chiptemperatur.

| Parameter | Symbol | Wert |

|---|---|---|

| Betriebsspannung | UN | 70 V |

| Nennstrom | IN | 30 A |

| Drain-Source Widerstand bei Chiptemperatur: 125°C Gatespannung: 10V |

RDSon | 17 mΩ |

| Pulsbreite | ton | 150 µs |

| Schaltfrequenz | ƒschalt | 5 kHz T = 200µs |

| Einschaltzeit (risetime) | tr | 500 ns |

| Ausschaltzeit (falltime) | tƒ | 800 ns |

Leitend-Verluste

Während der FET bei PWM-Ansteuerung eingeschaltet ist, erzeugt er Verlustleistung.

[math]\displaystyle{ P_\text{ON} = {I_\mathrm{N}}^2 \cdot R_\mathrm{DS_\mathrm{ON}} \cdot \frac{t_\mathrm{ON}}{T} = 30^2A^2 \cdot 17m\Omega \cdot \frac{150\mu s}{200\mu s} = 11{,}5W }[/math]

Schalt-Verluste

Vereinfachter Ansatz.

Einschalten:

- [math]\displaystyle{ \begin{align} P_\mathrm{SW_r} &= \tfrac14 \cdot U_N \cdot I_N \cdot \frac{t_r}{T} \\ &= \tfrac14 \cdot 70V \cdot 30A \cdot \frac{500ns}{200\mu s}=1{,}3W \end{align} }[/math]

Ausschalten:

- [math]\displaystyle{ \begin{align} P_\mathrm{SW_f} &=\tfrac14 \cdot U_N \cdot I_N \cdot \frac{t_f}{T}\\ &=\tfrac14 \cdot 70V \cdot 30A \cdot \frac{800ns}{200\mu s}=2{,}1W \end{align} }[/math]

Alternativ und genauer kann man rechnen, wenn die Ein- Ausschaltenergie im Datenblatt angegeben ist. Aber Achtung! Die Randbedingungen unter denen die genannte Energie ermittelt wurde, müssen genau so zutreffen.

- [math]\displaystyle{ \begin{align} P_{SW_f} = f_{schalt} \cdot E_{ON} \end{align} }[/math]

- [math]\displaystyle{ \begin{align} P_{SW_r} = f_{schalt} \cdot E_{OFF} \end{align} }[/math]

Die Gesamtverlustleistung beträgt also in etwa 15W.

Damit muß ein entsprechender Kühlkörper ausgelegt und die Chiptemperatur berechnet werden. z. B.:

- Kühlkörper mit einem R_th von 0,2K/W

- max. Umgebungstemperatur +60°C

- R_th "junction-case" des FETs 0,8K/W

- R_th der Wärmeleitfolie zwischen FET und Kühlkörper ca. 2,0K/W

- R_th gesamt: 3,0K/W

- Bei einer Verlustleistung von 18W und einer Umgebungstemperatur von 60°C hat der Chip eine Temperatur von ca. 18W * 3,0K/W +60°C = 114°C. ==> o.k.!

Unter Berücksichtigung der Tatsache, daß hier viele Vereinfachungen vorgenommen, und die Art der Last nicht beachtet wurde ist es sinnvoll, einen gewissen Sicherheitsabstand zu den zulässigen Maximalwerten einzuhalten. Daher ist es empfehlenswert, die Chiptemperatur auf ca. 125°C zu beschränken.

Des Weiteren ist hier die parasitäre Diode im FET nicht berücksichtigt. Wenn während der "off" Zeit ein Strom über die Diode fließt (Reverse recovery current oder Freilaufstrom), muß die dadurch zusätzlich entstehende Verlustleistung in die obige Berechnung der maximalen Chiptemperatur mit einfließen.

Treiberleistung

Auch wenn der MOSFET ein spannungsgesteuertes Bauelement ist, muss trotzdem bei jedem Einschalten und bei jedem Ausschalten die Gatekapazität umgeladen werden. Bei älteren Leistungs-FET - oder bei einem schlechten Design (!) - muss sogar teilweise mit negativer Spannung am Gate gearbeitet werden, um eine vollständige Sperrung zu erreichen. Diese Umladung muss möglichst schnell erfolgen, um die Verluste im FET während der Umschaltphase zu minimieren. Dazu findet ein MOSFET-Treiber Verwendung. Hier eine detaillierte Beschreibung zum Treiber.

Da die Gatekapazität nicht direkt im Datenblatt enthalten ist kann man sich mit der Eingangskapazität Ciss behelfen. Im Arbeitspunkt ist die Gatekapazität ungefähr 5x größer als der im Datenblatt für Ciss angegebene Wert. Daher berechnet sich die Treiberleistung wie folgt:

- [math]\displaystyle{ P_\text{Treiber} = C \cdot U^2 \cdot f = 5 \cdot C_\text{íss} \cdot U_\text{Gate}^2 \cdot f_\text{schalt} }[/math]

1.Beispiel, kleine MOSFET-Steuerung mit niedriger Leistung und Frequenz.

- [math]\displaystyle{ P_\text{treiber} = 5 \cdot 4{,}8\,\text{nF} \cdot 15\,\text{V}^2 \cdot 10\,\text{kHz} = 54\,\text{mW} }[/math]

2.Beispiel, sehr große MOSFET-Steuerung für Induktionsheizung mit sehr hoher Leistung und Frequenz.

- [math]\displaystyle{ P_\text{treiber} = 5 \cdot 24\,\text{nF} \cdot 15\,\text{V}^2 \cdot 250\,\text{kHz} = 6{,}75\,\text{W} }[/math]

Aber Achtung, so ein MOSFET-Treiber hat auch einen Eigenverbrauch, der leicht zwischen 0,5 und 1 W liegen kann.

Bei niedrigen PWM-Frequenzen kann man Logic Level MOSFETs auch direkt per CMOS-Ausgang ansteuern, z.B. mit einem AVR, wie in diesem Forumsbeitrag zu sehen ist.

Low- und High-Side

Definition LS- und HS:

- Low-Side Schalter

- Der FET schaltet eine Last gegen GND - auch als LS-Schalter bezeichnet.

- High-Side Schalter

- Der FET schaltet eine Last an die Versorgungsspannung – auch als HS-Schalter bezeichnet.

Anregungen oder Fragen auch gerne per Email an Powerfreak. Dieser Artikel kann dadurch regelmäßig erweitert und ggf. durch ein FAQ ergänzt werden.

SOA Diagramm

SOA-Diagramm (engl. Safe Operating Area, sicherer Arbeitsbereich) beschreibt die zulässige Verlustleistung eines Transistors in Anhängigkeit des Drainstroms (I_D), der Drain-Source Spannung (U_DS) und der Pulsbreite. Als Beispiel sei hier der BUZ 11 genannt. Im nachfolgenden Diagramm ist das SOA-Diagramm dargestellt. Wie ist es zu verstehen? Zunächst gibt es eine Grenze auf der linken Seite, die schräge, dunkelblaue Line. Diese wird durch den minimalen R_DS_ON festgelegt, hier wirkt der MOSFET wie ein ohmscher Widerstand. Mehr Strom kann bei einer bestimmten Spannung nicht fließen. Die zweite Grenzlinie ist ganz rechts die pinkfarbene Linie, sie stellt die maximale Sperrspannung des MOSFET dar. Die dritte Grenze ist der maximal zulässige Drainstrom, hier im Beispiel 120A, dargestellt durch die gelbe Linie. Die maximale Spannung zwischen Drain und Source sowie der Drainstrom sind abhängig von der Pulsbreite, mit welcher der MOSFET betrieben wird. Bei nur 2,5µs Pulsbreite (Rechteckimpuls) müssen die beiden Parameter sich innerhalb der Fläche bewegen, welche durch die dunkelblaue, gelbe und die pinkfarbene Line begrenzt wird. Im Extremfall dürfen 50V anliegen und 120A fließen, das sind satte 6kW Pulsleistung! Werden die Pulse breiter, so sinken die zulässigen Ströme und Spannungen, bei 1ms (dunkelblaue Linie bis zur braunen Linie, dann zur pinkfarbenen Linie) sind maximal noch 50V und 7A zulässig, also nur noch 350W. Die letzte Linie stellt den Fall für Gleichstrom (engl. Direct Current), also Dauerbelastung dar, hier sind bei 50V maximal 1,5A zulässig, was einer Dauerverlustleistung von 75W entspricht. MOSFETs, welche nur für Schaltbetrieb und nicht für Linearbetrieb geeignet sind, haben keine Kennlinie für DC. Im normalen Schaltbetrieb liegt der Arbeitspunkt auf der linken Grenzlinie R_DS_ON_MIN. Nur im Linearbetrieb liegt der Arbeitspunkt innerhalb der Fläche, welche durch die Außenlinien begrenzt wird.

Bei der Anwendung des Diagramms gilt es einiges zu beachten. Die Pulsleistungen sind nur zulässig, wenn der MOSFET vorher kalt ist, sprich ca. 25°C Sperrschichttemperatur hat. War er vorher schon heiß, reduziert sich die zulässige Belastung deutlich. Ebenso dürfen die Pulse nicht zu schnell wiederholt werden, denn dann ist der MOSFET noch vom vorherigen Puls aufgeheizt. Im Fall von DC sind 75W Verlustleistung auch eher ein theoretischer Wert, welcher real nur schwer erreicht werden kann, wenn der MOSFET auf einem sehr großen Kühlkörper optimal montiert ist. Praktisch liegen die erreichbaren Werte eher bei der Hälfte.

(Anm. Eigentlich müsste für die R_DS_ON Grenzlinie R = U / I der minimale R_DS_ON rauskommen, hier ~40mOhm, es kommen aber ~80mOhm raus. Die Ursache dafür ist unklar, möglicherweise liegt hier ein Sicherheitsfaktor zu grunde).

Linearbetrieb von MOSFETs

Der Großteil der Anwendungen nutzt MOSFETs als Schalter, d.h. der MOSFET ist entweder voll gesperrt oder voll durchgesteuert. Dafür gelten auch all die Hinweise in diesem Artikel. In bestimmten Anwendungen werden MOSFETs aber auch im Linearbetrieb eingesetzt, z.B in linearen Endstufen für Audio, Video, elektronischen Lasten und Stromquellen. Hier muss man einiges beachten. Ein verbreiteter Irrtum besteht darin zu glauben, MOSFETs könne man im Linearbetrieb einfach parallel schalten, weil der positive Temperaturkoeffizient von [math]\displaystyle{ R_{DS(ON)} }[/math] eine Symmetrierung bewirkt, ähnlich den Emitterwiderständen bei parallelgeschalteten Bipolartransistoren. Das ist ausschließlich im Schaltbetrieb möglich, und daher falsch! Im Linearbetrieb spielt der Temperaturkoeffizient von [math]\displaystyle{ R_{DS(ON)} }[/math] keine Rolle, weil der MOSFET selten bis nie komplett durchgesteuert ist. Eben darum ist beim Linearbetrieb der minimale [math]\displaystyle{ R_{DS(ON)} }[/math] in den meisten Fällen unwichtig und man kann auch eher hochohmige, ältere MOSFETs verwenden, wie z.B. den BUZ11.

Hier wirkt vielmehr der negative Temperaturkoeffizient (TK) der Thresholdspannung [math]\displaystyle{ U_{GS(thr)} }[/math], vergleichbar dem negativen TK der Basis-Emitter-Spannung von Bipolartransistoren. D.h. mit steigender Temperatur und konstanter Gate-Source-Spannung steigt der Stromfluss der Drain-Source Strecke. In einer Parallelschaltung von MOSFETs würde dies bedeuten, dass der MOSFET mit dem geringfügig größeren Drainstrom (Fertigungstoleranzen) wärmer wird, was zu einem weiter steigenden Drainstrom und damit noch mehr Wärme führt. Damit ist die Schaltung thermisch instabil und würde zum Durchbrennen der MOSFETs führen, einer nach dem Anderen.

Um das zu verhindern muss man relativ große Ausgleichswiderstände in die Source-Leitung der einzelnen MOSFETs schalten, um diese Drift zu kompensieren. Dadurch verschlechtert sich natürlich der Wirkungsgrad des Verstärkers. MOSFETs haben einen TK von typisch -5mV/K für [math]\displaystyle{ U_{GS(thr)} }[/math], das ist mehr als das doppelte von Bipolartransistoren mit typisch -2mV/K, weshalb die Symmetrierungswiderstände mehr als doppelt so groß sein müssen. Weiterhin muss man beachten, dass die Toleranzen von [math]\displaystyle{ U_{GS(thr)} }[/math] sehr groß sind, im Bereich von Volt! Das kann man sinnvoll nicht mehr mit Gatewiderständen symmetrieren, hier muss man die MOSFETs ausmessen und Gruppen mit geringen Toleranzen in einer Schaltung verwenden (engl. matching).

Eine andere Möglichkeit ist die getrennte Ansteuerung der einzelnen MOSFETs, das wird oft in elektronischen Lasten bzw. Konstantstromquellen gemacht. Hier treten keine zusätzlichen Verluste auf und der Mehraufwand in der Ansteuerung ist meist unkritisch.

Weiterhin muss man beachten, dass viele der heutigen HochleistungsMOSFETs intern eine Parallelschaltung vieler kleiner MOSFET-Zellen (z.B. sogenannte Trench-FET) sind, und somit oft für den Linearbetrieb ungeeignet sind. Denn auch dort können einzelne Zellen überhitzen und durchbrennen (Hot Spot). Ob ein MOSFET für den Linearbetrieb tauglich ist steht manchmal im Datenblatt, oft aber eher nicht, eben weil die meisten MOSFETs als Schalter entwickelt und gebaut sind. Typische Vertreter für Linearbetrieb findet man in der MOSFET-Übersicht. Ein wichtiges Indiz für Linearbetrieb ist eine Kurve für DC im SOA-Diagramm. Meist geht es dort nur bis 10ms, DC fehlt, eben weil DC (engl. Direct Current = Gleichstrom = Linearbetrieb) nicht zulässig ist. Manchmal hat der Hersteller auch "vergessen", die Kennlinie für DC mit reinzuschreiben, wie z.B. bei IRF, wie in diesem Beitrag zu erfahren ist. Ein recht gutes Indiz dafür, ob ein FET für den Linearbetrieb taugt, ist die Vorwärtssteilheit. Diese kennzeichnet die Abhängigkeit des Drainstromes von der Ansteuerung am Gate als [math]\displaystyle{ S = \Delta i_d/\Delta u_{gs} }[/math]. Moderne Trench-FET erreichen heute Steilheiten im dreistelligen Bereich und sind für Linearanwendungen völlig unbrauchbar. Zum Vergleich: Der BUZ11 kommt mit gerade einmal 4 bis 5 Siemens daher.

In diesem Beitrag wird die DC-Linie im SOA-Diagramm noch genauer erklärt: Re: MOSFET Linearbetrieb möglich?

Siehe auch

- Leistungselektronik

- Mosfet-Übersicht

- IGBT

- TRIAC

- Kühlkörper

- Zwischenkreiskapazität

- Treiber

- Wie schließe ich einen Mosfet an einen Mikrocontroller an?

- Übersicht H-Brücken

- Forumsbeitrag: MOSFETs im Linearbetrieb

- Forumsbeitrag: nochmal MOSFETs im Linearbetrieb

- Forumsbeitrag: sehr ausführlicher Forumsbeitrag über MOSFETs im Linearbetrieb. Berücksichtigt auch den Spirito-Effekt.

- Forumsbeitrag: Über eine elektronische Last, sehr lang

- Forumsbeitrag: Logic Level MOSFETs direkt mit einem AVR treiben.

- Forumsbeitrag: MOSFETs im Linearbetrieb, Laborerfahrungen

- Forumsbeitrag: MOSFETs für Linearbetrieb

- Forumsbeitrag: Verpol- und Überspannungsschutz mit MOSFETs

- Forumsbeitrag: Linearbetrieb von MOSFETs

Weblinks

- Feldeffekttransistoren bei elektronikinfo.de

- FET im ELKO

- MOSFET im ELKO

- MOSFET bei sprut.de

- MOSFETs in Audioendstufen, engl.

- FAQ Answer ID 214 bei IRF zum Linearbetrieb

- AN11158 - Understanding power MOSFET data sheet parameters von NXP (PDF)

- TN00008 - Power MOSFET frequently asked questions and answers von nexperia (PDF)

- AN: Linear Mode Operation andSafe Operating Diagram of Power-MOSFETs von Infineon (PDF)

- MOSFETs Withstand Stress of Linear-Mode Operation Neuentwickelte MOSFETs für Linearbetrieb (PDF)